# **TSV development for miniaturized MEMS acceleration switch**

Nicolas Lietaer<sup>1</sup>, Anand Summanwar<sup>1</sup>, Thor Bakke<sup>1</sup>, Maaike Taklo<sup>1</sup>, Per Dalsjø<sup>2</sup>

<sup>1</sup> SINTEF ICT, Norway <sup>2</sup> Norwegian Defence Research Establishment (FFI), Norway

IEEE 3DIC conference, November 16-18, 2010, Munich, Germany

#### Abstract

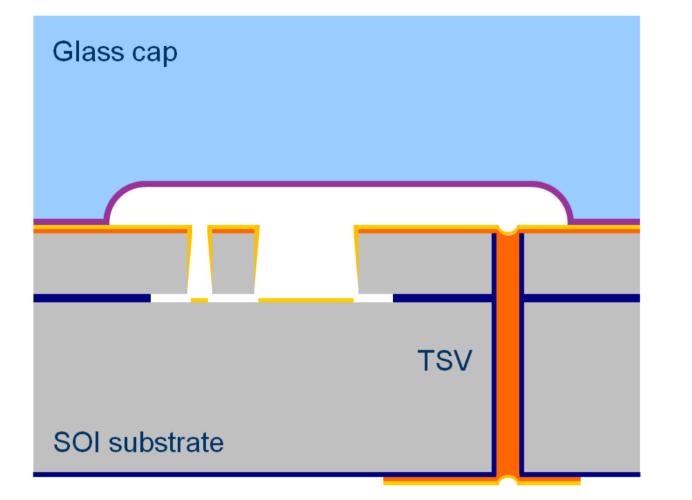

This poster presents a new concept for fabricating a MEMS acceleration switch with through silicon vias (TSVs) through the SOI (silicon on insulator) device wafer. Results of the short-loop experiments conducted in order to develop the most critical process steps are shown. The use of TSVs significantly simplifies the mounting of the MEMS devices and it results in the smallest footprint.

## Concept

If subjected to a sufficient acceleration, the released silicon structure will move in the lateral direction and make contact with the sidewall of a neighbouring structure, thereby opening or closing a circuit.

## **TSV** etching

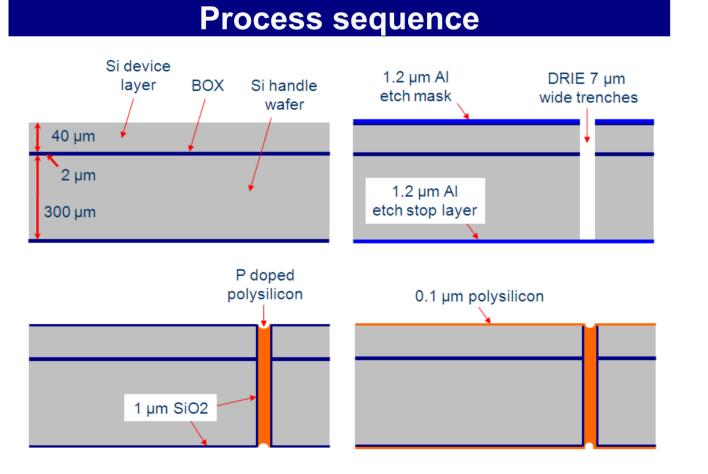

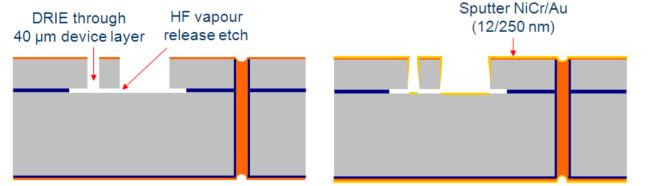

Deep reactive ion etching (DRIE) is used to etch 7 x 70  $\mu$ m trenches consecutively through the 40  $\mu$ m silicon device layer, 2  $\mu$ m buried oxide (BOX) and 300  $\mu$ m silicon handle wafer. This results in an aspect ratio close to 50:1. The etch tool that is used is an Alcatel AMS200SE I-Productivity silicon etcher.

## TSV filling, etchback and metallisation

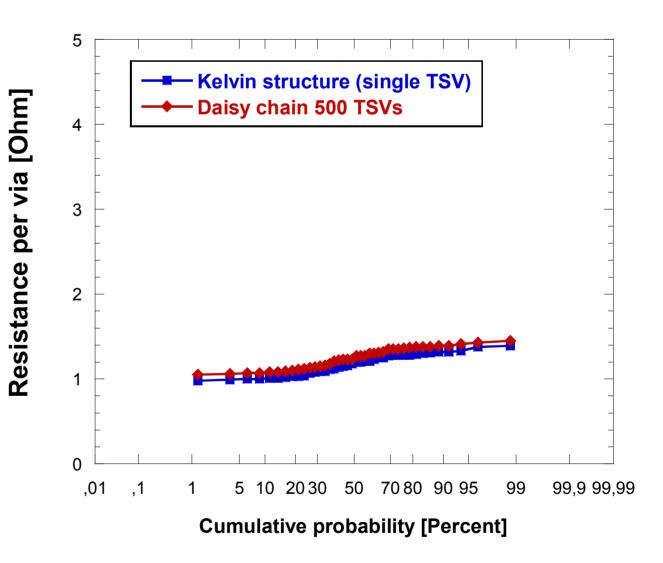

TSVs with a width of 7  $\mu$ m were etched through 300  $\mu$ m thick silicon wafers (aspect ratio 42:1). The vias were isolated from the bulk silicon by thermal oxide and filled with phosphorus doped polysilicon.

## Fig. 1 : Schematic cross-section of the MEMS acceleration switch with TSV.

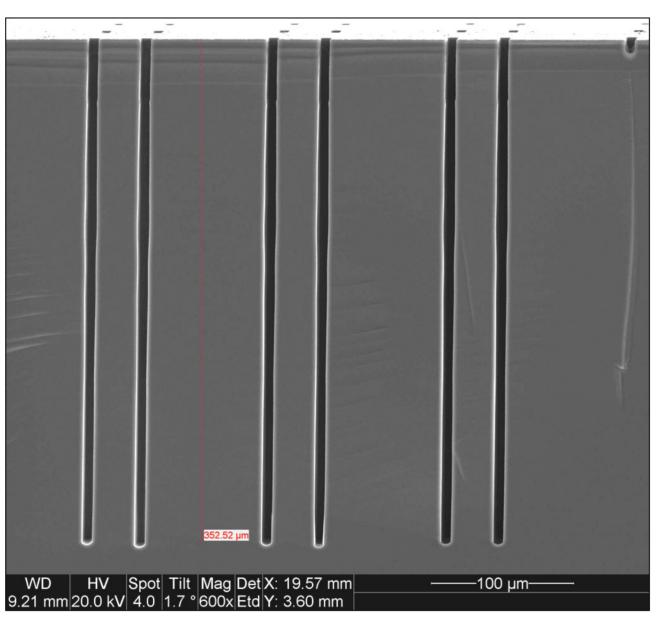

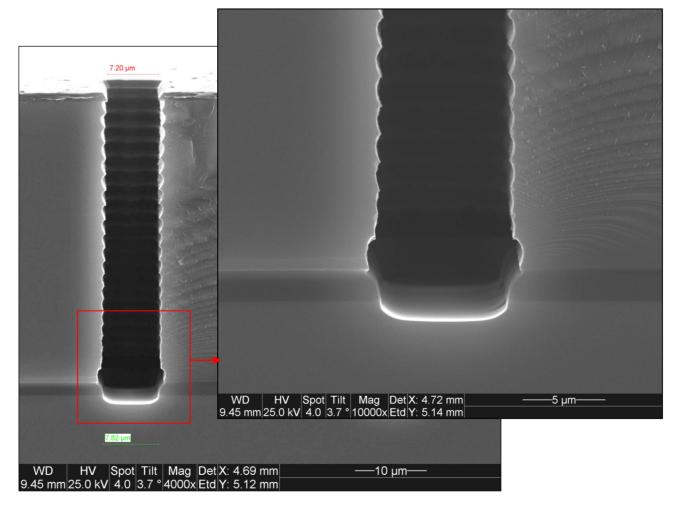

Fig. 3 : SEM cross-section of a bulk silicon test wafer after performing the device layer DRIE followed by the handle wafer DRIE.

A major challenge is the etching of the 2  $\mu$ m thick BOX layer at the bottom of trenches that are 40  $\mu$ m deep and only 7  $\mu$ m wide. A new etch recipe was succesfully developed for this purpose.

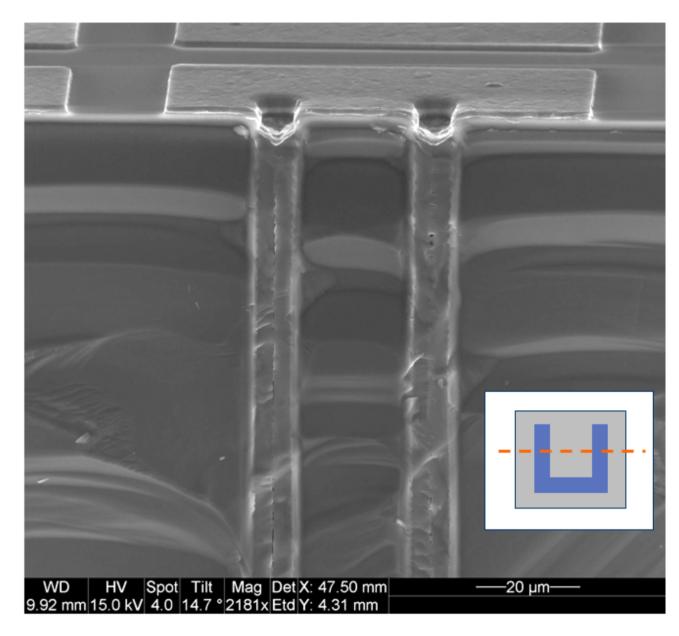

Fig. 5 : SEM cross-section of a U-shaped TSV structure after patterning of the metallization.

Following etchback of the polysilicon, metal deposition and patterning, the TSVs showed excellent electrical results and high yield.

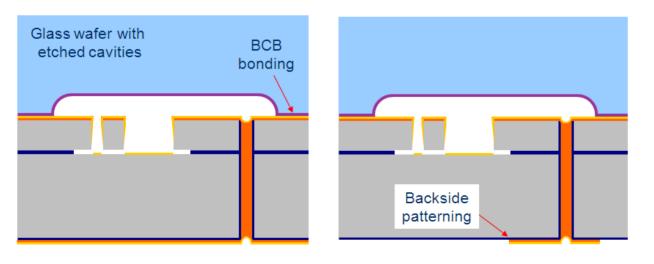

Fig. 2 : Proposed process sequence for the miniaturized acceleration switch.

Fig. 4 : SEM cross-section of an SOI wafer after etching 7 x 70  $\mu$ m trenches through the 40  $\mu$ m silicon device layer and 2  $\mu$ m BOX.

#### Acknowledgment

This work was supported by the European ENIAC Joint Undertaking project ID:120016 JEMSIP-3D.

Fig. 6 : Resistance per via for 7  $\mu$ m narrow U-shaped TSV structures with a cross-section area of 1069  $\mu$ m<sup>2</sup>.

## Conclusions

A novel concept is proposed for fabricating a miniaturized acceleration switch. The most critical process steps for realizing TSVs through the MEMS device wafers were successfully developed. Processing of a complete demonstrator as shown in Fig. 1 is ongoing.

**Technology for a better society**