### **3D Interconnect Technologies For Advanced MEMS/NEMS applications**

- supported by the European Commission under support-no. IST-026461 e-CUBES and ENIAC support-no. 120016 JEMSiP-3D

Nicolas Lietaer, Maaike M. V. Taklo, Kari Schjølberg-Henriksen : SINTEF, Norway Peter Ramm: Fraunhofer-IZM, Munich, Germany

#### 216<sup>th</sup> ECS meeting, Vienna October 4-9, 2009

## Outline

- 3D Integration

- Motivation

- Evolution

- Key processes

- 3D Integration of MEMS/NEMS and IC

- More than Moore

- Key market driver

- Specific challenges for MEMS/NEMS

- 3D Technologies for integration of MEMS/NEMS and IC

- TSVs for MEMS

- Bonding of MEMS and IC

- Technology demonstrators

- Summary

# **3D integration**

- Motivation

- Miniaturization

- Increased interconnect speed

- Reduced RC delays

- Reduced power consumption

- Reduced overall costs

- Increased yield and reliability

- Reduced weight

- Increased functionality

### Evolution

- Multi chip modules (not 3D)

- 3D packaging : chip scale stacking without through silicon vias

- 3D integration : through silicon vias (TSV), wafer level bonding

#### multi chip module (MCM) Int. Sensor Systems, Inc

#### System in package (SiP) Toshiba

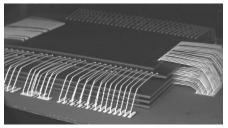

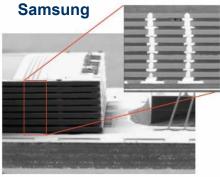

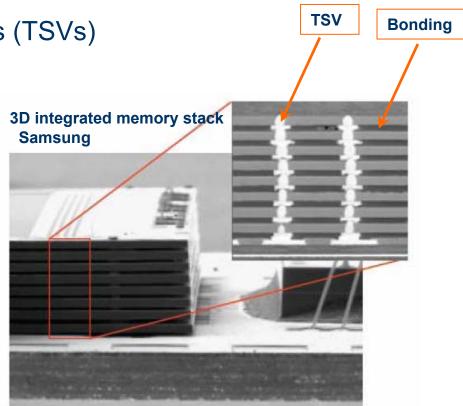

#### **3D integrated memory stack**

# **3D integration**

### Key processes

- Through silicon/substrate vias (TSVs)

- Electrical interconnects through the chips

#### Bonding

Mechanical and electrical interconnection between the chips in the IC stack

## Outline

### 3D Integration

- Motivation

- Evolution

- Key processes

- 3D Integration of MEMS/NEMS and IC

- More than Moore

- Key market driver

- Specific challenges for MEMS/NEMS

- 3D Technologies for integration of MEMS/NEMS and IC

- TSVs for MEMS

- Bonding of MEMS and IC

- Technology demonstrators

### Summary

# **3D integration of MEMS/NEMS and IC**

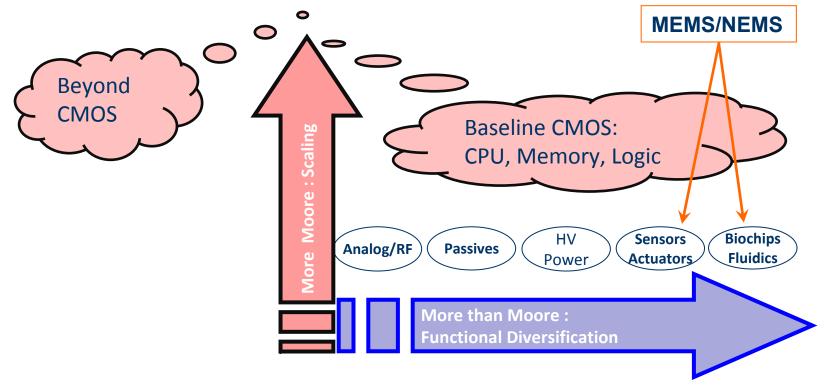

### More than Moore

■ Moore's Law scaling alone can not maintain the progress of smart systems → heterogeneous integration

Source : Dr. Peter Ramm Fraunhofer IZM Munich

216th ECS meeting, Vienna Oct 4-9, 2009

## **3D integration of MEMS/NEMS and IC**

Key market driver : portable consumer electronics

- Cell phones, PDAs, laptops, game controllers (e.g. Nintendo Wii, PS3), etc

- New functionality based on MEMS : drop detection, motion sensor, etc

- Requirements : small size, low cost, low power

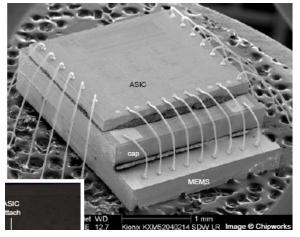

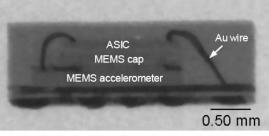

Kionix, KXPB5 3-axis accelerometer

ST Microelectronics, LIS331DL 3-axis accelerometer

Figure 9 STMicroelectronics LIS331DL Package X-Ray

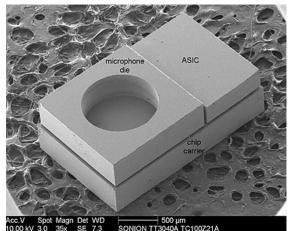

### Sonion, DigiSiMic digital MEMS microphone

#### Source : Chipworks

216th ECS meeting, Vienna Oct 4-9, 2009

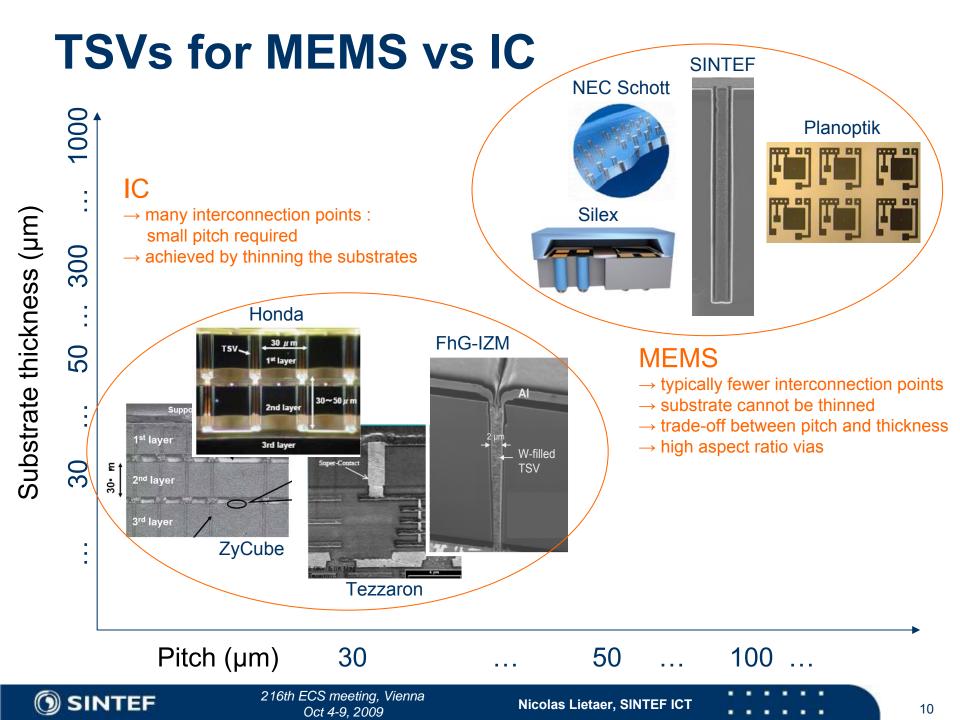

# **3D integration of MEMS/NEMS and IC**

#### Specific challenges for MEMS and NEMS

- Substrate thickness (300 to 1000 µm)

- MEMS structures rely on a certain mass/volume/thickness for stability/reliability/strength : the substrate cannot be thinned

- High aspect ratio etch is difficult -> trade-off thickness vs via pitch

- Substrate material

- Anodic bonding of glass-to-silicon wafers is commonly used for reliable hermetic sealing of MEMS -> DRIE not possible

- MEMS or often fabricated on SOI wafers -> complicates DRIE

- Wet processing for devices with inlets/released structures

- Wet etching and cleaning, electroplating, etc can be problematic when inlets or released structures are present

- High topography

- MEMS devices often have high topography surfaces (e.g. inlets or movable parts) which can be a challenge for the processing

- Functional and nano materials with temperature limitations

- e.g. organic coatings on optical sensors

- Fragility of MEMS/NEMS structures

- Might not allow certain processes

## Outline

- 3D Integration

- Motivation

- Evolution

- Key processes

- 3D Integration of MEMS/NEMS and IC

- More than Moore

- Key market driver

- Specific challenges for MEMS/NEMS

- 3D Technologies for integration of MEMS/NEMS and IC

- TSVs for MEMS

- Bonding of MEMS and IC

- Technology demonstrators

- Summary

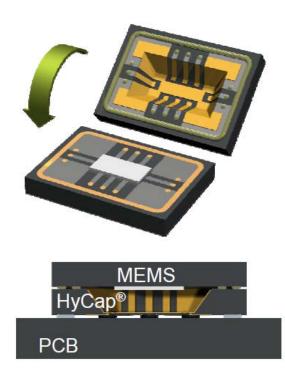

### Au vias through anisotropically wet-etched Si cap wafers Hymite

### HyCap®

- Anisotripically wet etched vias in Si wafer (KOH)

- No DRIE

- Electroplated Au metallization

#### www.hymite.com

216th ECS meeting, Vienna Oct 4-9, 2009

# Bulk Si TSVs isolated by a dielectric trench Silex

- Bulk Si TSVs

- Via first approach

- DRIE trenches in low resistivity wafer filled with SiO<sub>2</sub>

- allows high temperature post processing

- sub 50 μm min pitch for 300 to 600 μm thick Si wafers

Through Silicon Insulator Technology (TSI<sup>TM</sup>)

Metal vias with Au or Cu for RF MEMS (< 50 mOhm/via)</p>

#### www.silexmicrosystems.com

216th ECS meeting, Vienna Oct 4-9, 2009

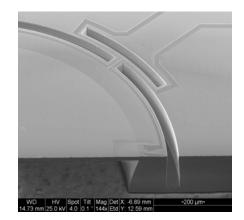

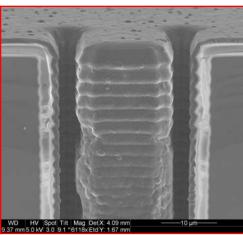

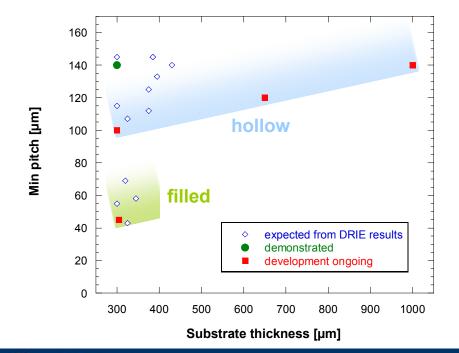

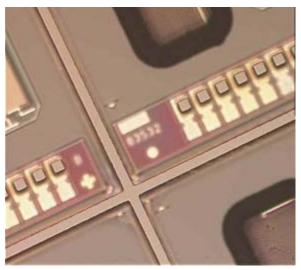

# Hollow and filled polySi TSVs SINTEF

- Via first approach

- allows high temperature post processing

- Dry-film resist for patterning of hollow vias

- TSV technology platform for MEMS and interposers being established

Min pitch vs substrate thickness

216th ECS meeting, Vienna Oct 4-9, 2009

**Nicolas Lietaer, SINTEF ICT**

-50 µm-

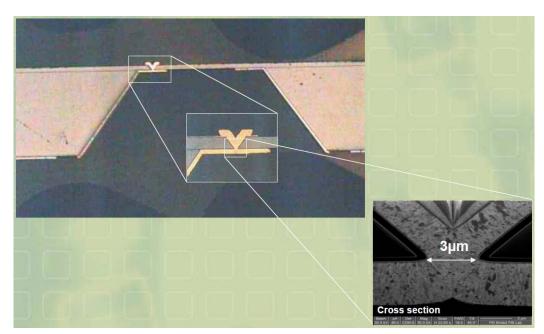

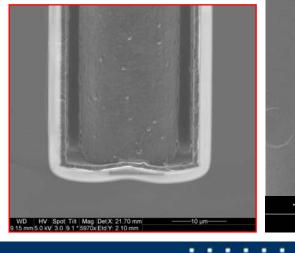

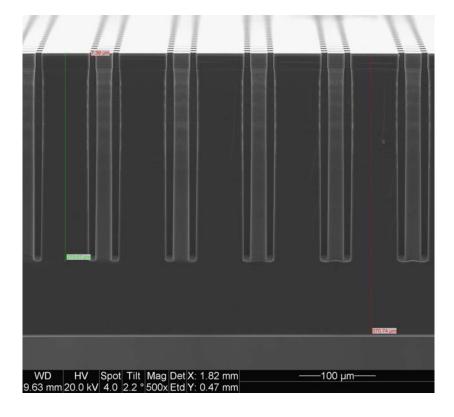

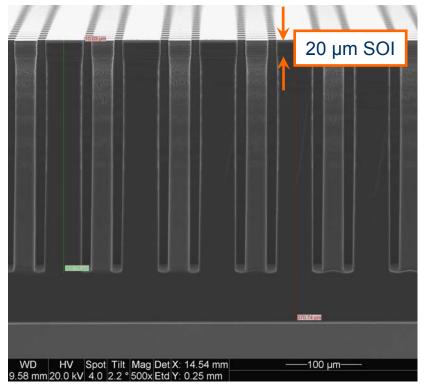

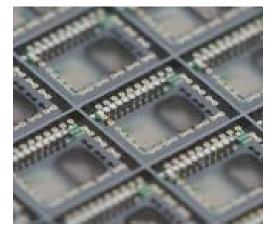

# Hollow and filled polySi TSVs for SOI wafers SINTEF

- polySi TSVs for SOI wafers under development

- DRIE 5  $\mu$ m wide structures through 20 and 43  $\mu$ m SOI layer  $\checkmark$

- BOX oxide etch development  $\checkmark$

- DRIE development ongoing

216th ECS meeting, Vienna Oct 4-9, 2009

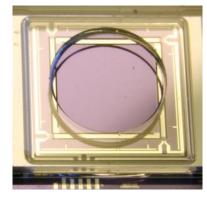

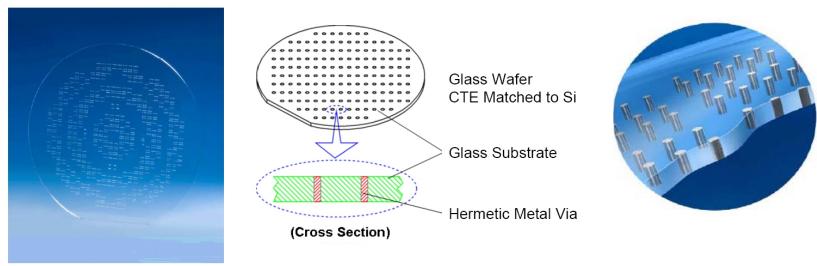

# Glass wafers with bulk silicon vias Planoptik

- Silicon glass compound wafers

- Hermetic vias and hermetic seal to sensor wafer

- Visual inspection possible

- Large design freedom

#### Source: SensoNor

Source: SINTEF

Source: SINTEF/Planoptik

216th ECS meeting, Vienna Oct 4-9, 2009

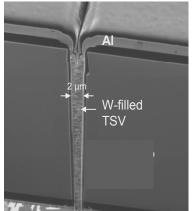

# Glass wafers with tungsten vias NEC Schott

- HermeS<sup>TM</sup>

- Tungsten TSVs in glass wafers

- Hermetic vias and hermetic seal to sensor wafer

- Visual inspection possible

- 300 μm min pitch for 500 to 600 μm thick glass wafers

### NEC / SCHOTT

Technology details of HermeS<sup>TM</sup> Glass substrate solution (Courtey of NEC Schott)

## Outline

- 3D Integration

- Motivation

- Evolution

- Key processes

- 3D Integration of MEMS/NEMS and IC

- More than Moore

- Key market driver

- Specific challenges for MEMS/NEMS

- 3D Technologies for integration of MEMS/NEMS and IC

- TSVs for MEMS

- Bonding of MEMS and IC

- Technology demonstrators

- Summary

. . . . . .

# Bonding of MEMS/NEMS and IC

### Selection criteria for bonding technology

- Chip-to-wafer or Wafer-to-wafer

- Interconnection pitch

- Number of I/O

- Dry/wet processing

- Alignment accuracy

- Stand-off height

- Hermeticity

- Reliability

- Cost

### Required : electrical and mechanical interconnection

# **Bonding of MEMS/NEMS and IC**

### Chip-to-wafer bonding

- Wafer size and chip size mismatch between MEMS and IC is not an issue

- Known good dies : lower yield of MEMS devices is not an issue

### Wafer-to-wafer bonding

- Simpler process

- More cost-effective (?)

- Better alignment accuracy

- Smaller min pitch

### Bump technologies : from solder balls to SLID

**Conventional solder balls** (solder paste screen printing) min pitch ~ 150 μm min stand-off ~ 80 μm **Au stud bumps** min pitch ~ 70 μm min stand-off ~ 10 μm **CuSn SLID** min pitch ~ 10 μm min stand-off ~ 10 μm

#### Jetted microbumps

min pitch ~ 80 μm min stand-off ~ 60 μm **Plated solder microbumps** min pitch ~ 25-50 μm min stand-off ~ 25 μm

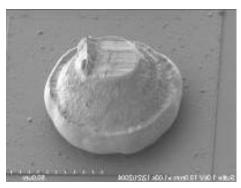

# Au stud bump bonding

- Chip to wafer

- Min pitch ~ 70 µm

- Stand-off height : ~ 10 20 μm

- No wet processing involved

- No need for UBM or passivation layers

- Most cost-effective for devices with lower I/O counts

- Demonstrated for stacking of MEMS onto ASIC (incl. reliability)

Source: Kulicke & Soffa

Source: SINTEF

### N. Lietaer, iMAPS Int Device Packaging Conf, 2009

216th ECS meeting, Vienna Oct 4-9, 2009

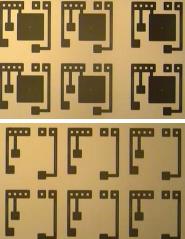

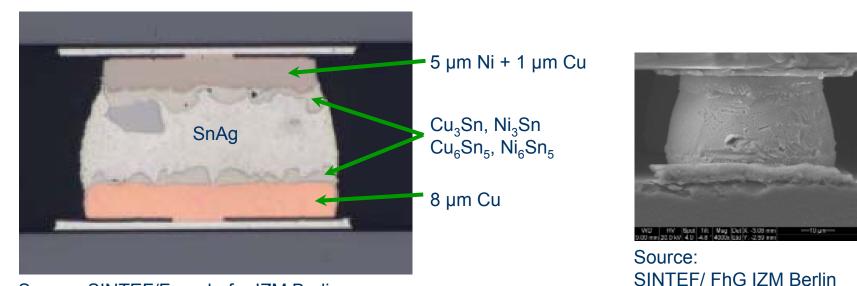

# Plated solder microbumps Example : SnAg

- Chip to wafer

- Min pitch 35-50 µm

- Stand-off height : < 30 μm</p>

- Misalignment < 2 µm</p>

- Passed extensive reliability tests

- Reliability tests

- 1000 cycles ÷ 40 150 °C

- 260°C 30 min

- 100% humidity, 121°C, 2 bar

- Electromigration

- High temperature storage

Source: SINTEF/Fraunhofer IZM Berlin

#### R. Johannessen, IEEE Trans Adv Pack, 2009

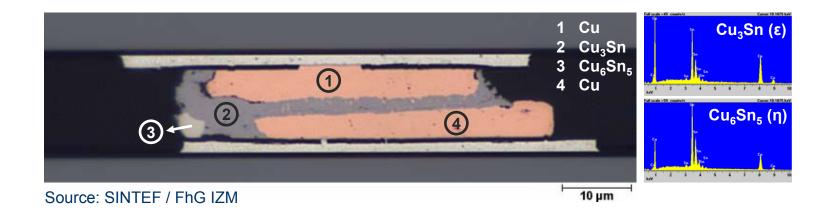

# Cu/Sn Solid-Liquid InterDiffusion (SLID)

- Chip to wafer

- Min pitch of 10 to 60 µm

- Stand-off height : ~ 10 μm

- Connection points :

5 x 5 µm to 30 x 30 µm

- Process :

- During bonding at 325°C, Sn melts

- Cu diffuses into the melted Sn layer to form  $Cu_6Sn_5(\eta)$  $\rightarrow$  the compound solidifies and the stack is fixed

- Cu<sub>6</sub>Sn<sub>5</sub> (η) then transforms into the thermodynamically stable Cu<sub>3</sub>Sn (ε) phase with melting point > 600°C

#### R. Wieland, RTI conference, 2005

# Anisotropic conductive adhesives/films (ACA/ACF)

- Chip to wafer

- Min pitch < 100 µm</p>

- Stand-off height < 10 μm</p>

- Temperature: 150 200 °C without custom-tailoring

- Feasibility study for MEMS/IC applications

- ACF with 5 µm Ø Ni/Au coated polymer spheres bonded at 180°C, 30s, varying pressure

#### 100 MPa (low range of pressure)

120 MPa (optimised process)

#### suitable deformation

SINTEF

216th ECS meeting, Vienna Oct 4-9, 2009

#### 140 MPa (too much pressure)

#### 160 MPa (too much pressure)

### Nguyen, IMAPS Nordic, 2009

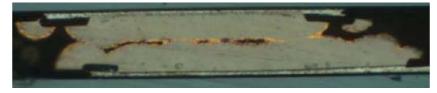

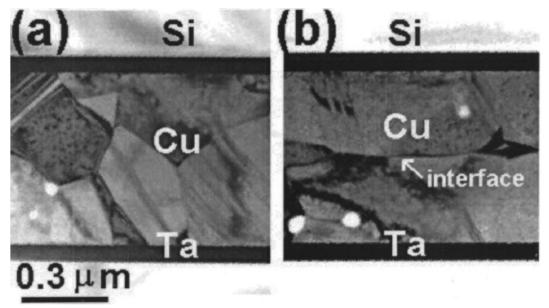

### **Metal thermocompression bonding**

- Cu, Au, Al

- Objective: recrystallisation

- Temperature, pressure, time

Bond: 350°C, 30 min Anneal: 350°C, 60 min Bond: 350°C, 30 min

K.N. Chen, Elchem Sol State Letters, 2004

216th ECS meeting, Vienna Oct 4-9, 2009

### Metal thermocompression bonding Example : Tezzaron Cu-Cu

- Chip to wafer

- Min pitch 25 µm

- 10 x 10 µm bond points

- Wafer to wafer

- Min pitch 2.4 µm

- 1.7 x 1.7 µm bond points

- Bond temperature 400°C

#### www.tezzaron.com

216th ECS meeting, Vienna Oct 4-9, 2009

## Outline

- 3D Integration

- Motivation

- Evolution

- Key processes

- 3D Integration of MEMS/NEMS and IC

- More than Moore

- Key market driver

- Specific challenges for MEMS/NEMS

- 3D Technologies for integration of MEMS/NEMS and IC

- TSVs for MEMS

- Bonding of MEMS and IC

- Technology demonstrators

- Summary

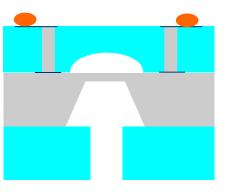

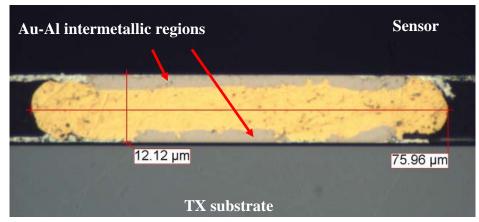

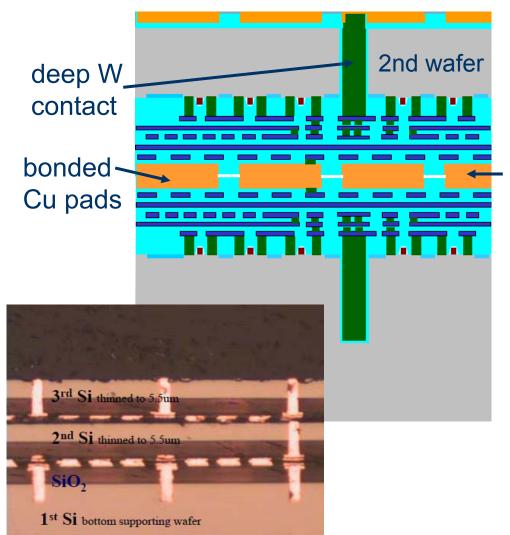

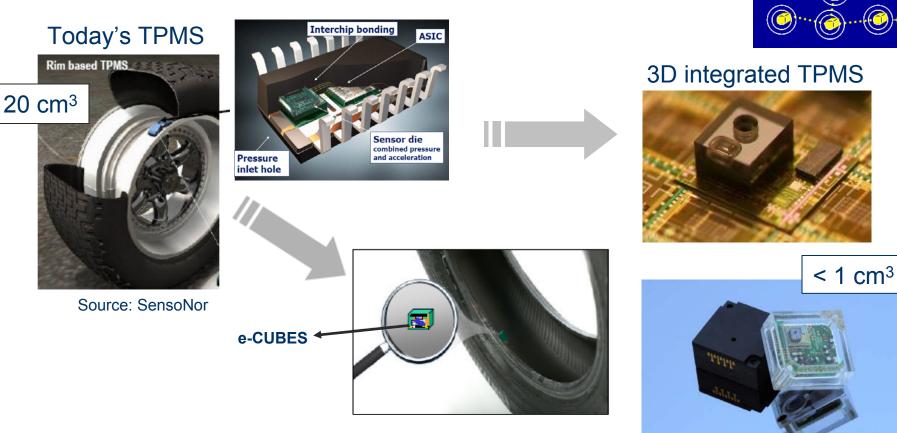

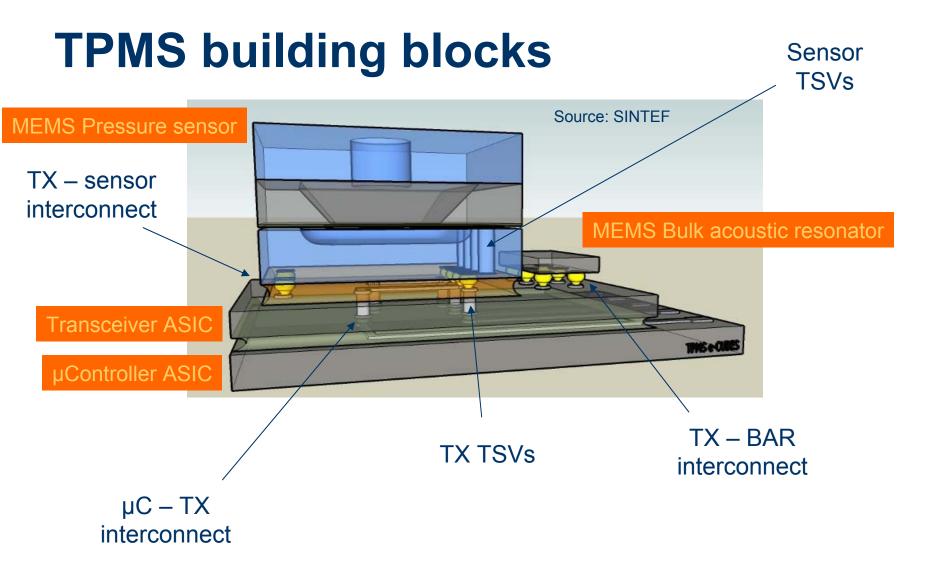

## e-CUBES automotive demonstrator

Automotive demonstrator : miniaturized Tire Pressure Monitoring System (TPMS)

### N. Lietaer, iMAPS Int Device Packaging Conf, 2009

216th ECS meeting, Vienna Oct 4-9, 2009

**Nicolas Lietaer, SINTEF ICT**

e-CUBES

$\bigcirc$

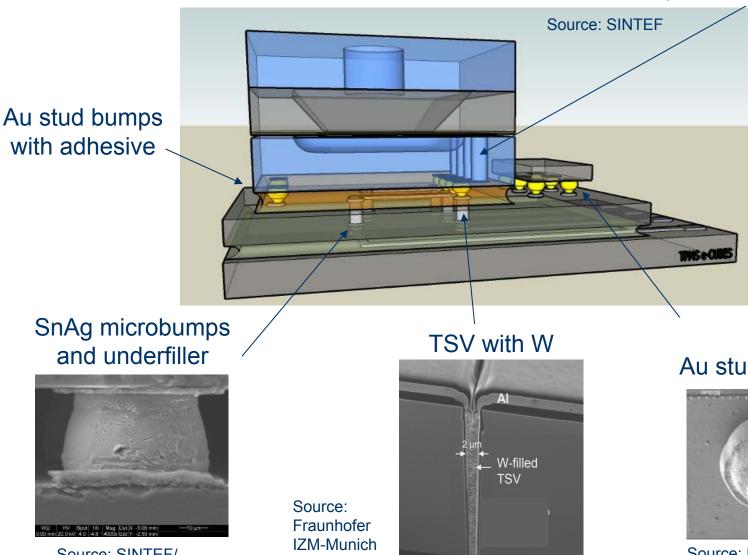

# **Technology choices**

#### Silicon-glass compound wafer with TSVs (alternative : hollow TSVs)

Source: SINTEF/ SensoNor/ PlanOptik

### SnAg microbumps

Source: SINTEF/ FhG IZM- Berlin

#### Au stud bumps only

Source: Kulicke & Soffa

216th ECS meeting, Vienna Oct 4-9, 2009

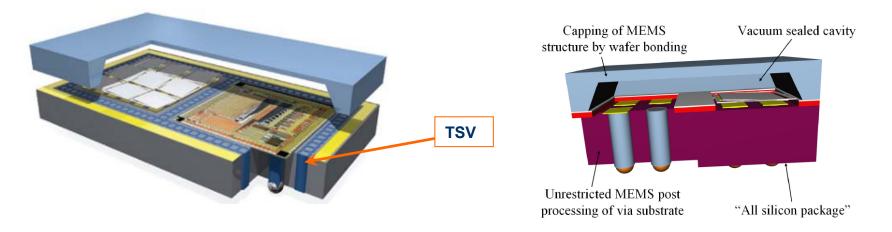

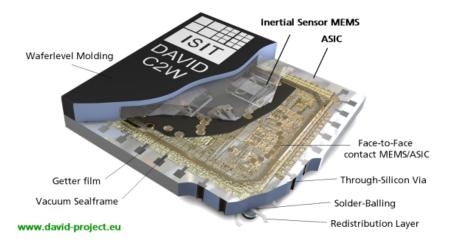

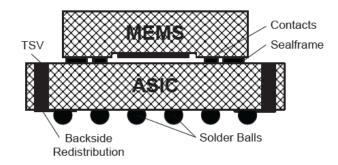

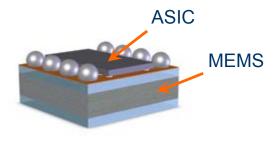

# **EU project DAVID**

- DAVID: Downscaled Assembly of Vertically Interconnected Devices

- provide extremely high packaging density for hybrid integration of MEMS with ASICs

#### Main technologies

- Post CMOS TSVs in ASIC

- Au-Sn bonding for the mechanical, hermetic and electrical joining of MEMS and ASIC

- Fine pitch solder balling

- Total package height < 1 mm</p>

### Chip-to-wafer

#### Wafer-to-wafer

#### http://www.david-project.eu/

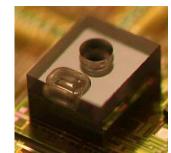

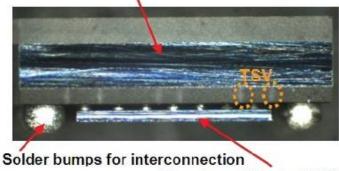

## **VTI technologies Chip-on-MEMS**

### Chip-to-wafer

Thinned ASIC IC flip-chipped to MEMS wafer with solder bumps

### Known good die

Total height < 1 mm</p>

#### Source: Chipworks / VTI

Hermetically sealed MEMS Sensing element

Signal conditioning ASIC

216th ECS meeting, Vienna Oct 4-9, 2009

Source: VTI

## Outline

- 3D Integration

- Motivation

- Evolution

- Key processes

- 3D Integration of MEMS/NEMS and IC

- More than Moore

- Key market driver

- Specific challenges for MEMS/NEMS

- 3D Technologies for integration of MEMS/NEMS and IC

- TSVs for MEMS

- Bonding of MEMS and IC

- Technology demonstrators

### Summary

## Summary

- There is an emerging market for 3D Integration of MEMS/NEMS and IC

- A number of challenges need to be adressed for fabricating TSVs through MEMS/NEMS structures, but solutions are being developed and demonstrated

- Metal bonding technologies used/developed for packaging and 3D integration of conventional ICs will also be applicable for 3D integration of MEMS/NEMS and IC

- Today, differences in wafer size, die size and yield make chip-to-wafer bonding the preferred approach for stacking of MEMS/NEMS and IC