# Latest Results From 2<sup>nd</sup> SINTEF 3D-Run

# **3D-Processing Meeting November 26, 2009**

T. E. Hansen, A. Kok, T. A. Hansen, N. Lietaer, G. U. Jensen, A. Summanwar

# Configuration geometries and estimated depletion voltage

| Substrate specific resistivity: $\geq$ 10000 $\Omega$ cm   |        |        |        |       |       |          |                    |  |

|------------------------------------------------------------|--------|--------|--------|-------|-------|----------|--------------------|--|

| Configuration                                              | ATLAS  |        |        |       |       | CMS 1ROC |                    |  |

|                                                            | 1E     | 2E     | 3E     | 4E    | 5E    | 2E       | 4E                 |  |

| n - p electrode<br>distance (µm)                           | 201    | 106    | 76     | 54    | 47    | 64       | 46                 |  |

| Max depletion<br>voltage planar<br>model                   | 40.5 V | 11.3 V | 5.8 V  | 2.9 V | 2.2 V | 2.2 V    | 4.1 V              |  |

| Max depletion<br>voltage square<br>cell model <sup>1</sup> | 190 V  | 32 V   | 11.8 V | 3.9 V | 2.4 V | 6.9 V    | 2.4 V <sup>2</sup> |  |

<u>1.</u> V. Eremin, E. Verbitskaya, "Analytical Approach for 3D Detectors Engineering", 2008 IEEE Nuclear Science Symposium conference Record

ICT

2. Square cell model should apply well to 1ROC 4E configuration

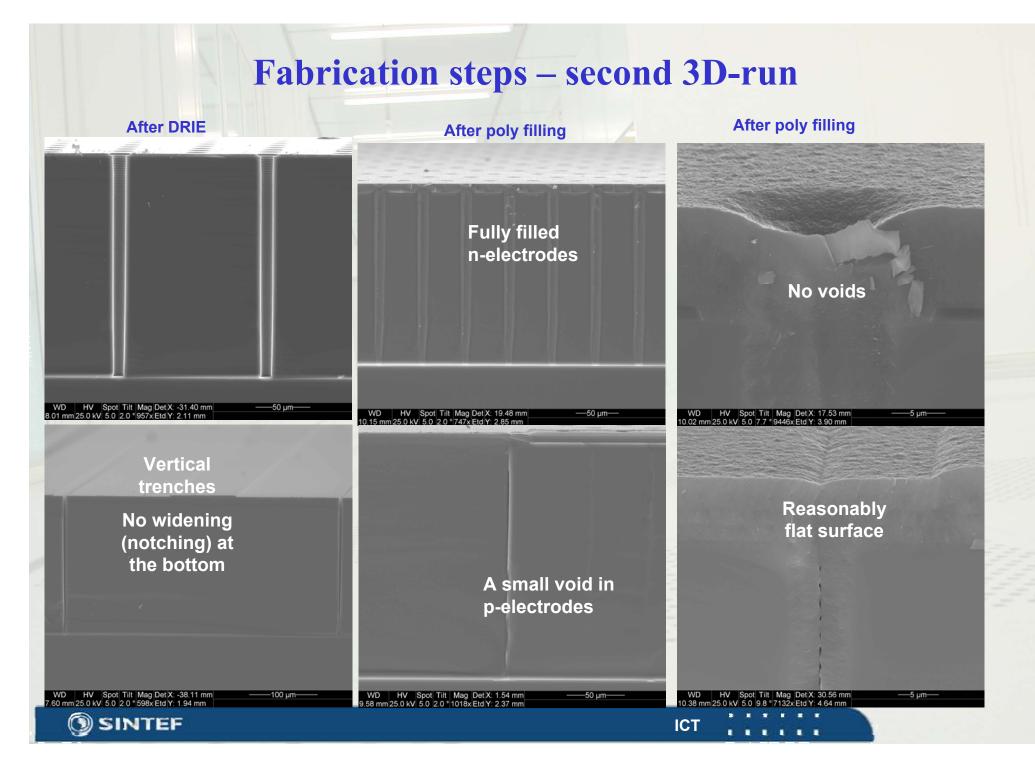

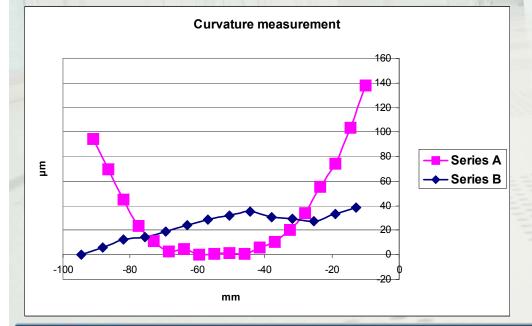

### SINTEF 3D: Series B improvements

#### **P-type wafers**

- Active edge will serve as depletion stop

- More robust configuration

Narrower trenches (4 μm)

Improved hole profiles

Extra nitride layer

- A better doping barrier

- Protects the field oxide

- Keeps symmetry on both back and front side

**Result of improvements**

Much reduced stress, bow and breakage

Wafer yield: 18 out of 23

ICT

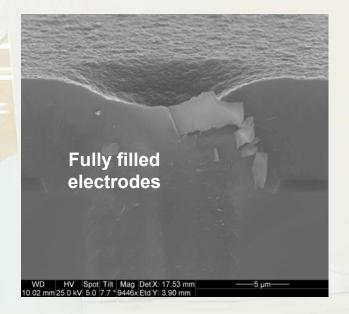

Improved electrode filling reduce topography and allow easier and better lithography

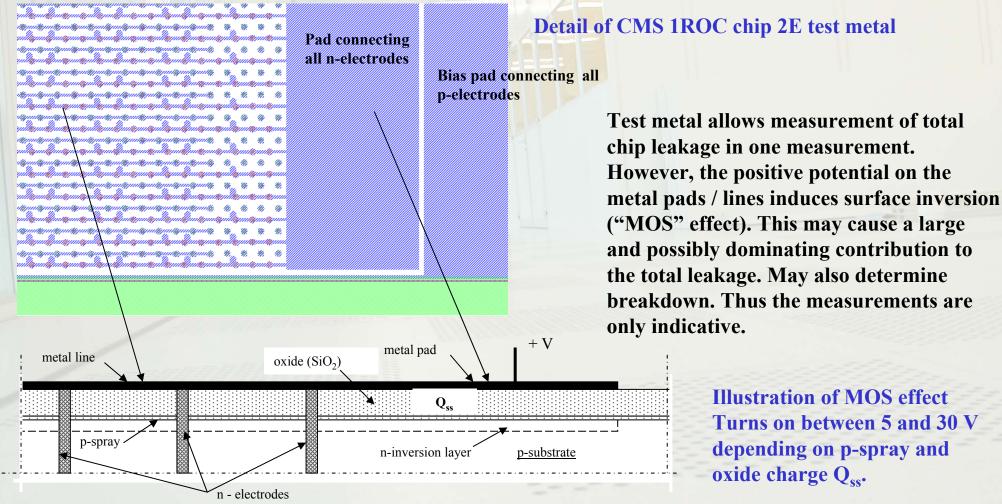

### **Test metal for electrical measurement**

#### Short circuits all n-electrodes. Later removed and replaced by final metal

SINTEF

#### **Detail of CMS 1ROC chip 2E test metal**

ICT

8

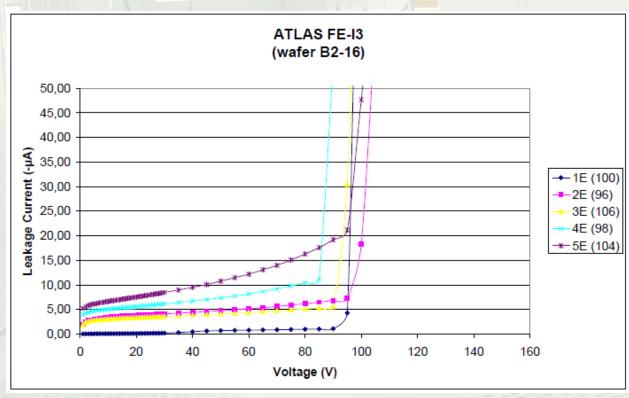

### **Measured IV-characteristics ATLAS FE-I3 chips**

Summary of measurements of good chips on wafer B2-16 (200 µm thick). Measured with

test metallization which short circuits all pixels (n-electrodes).

ICT

Total leakage from  $\approx$  2700 pixels as function of bias. Corresponds to  $\approx$  2700 (1E) to  $\approx$  13500 (5E) electrodes. Leakage Includes "MOS" effect and possible bad electrodes.

Yield of chips measured on all on wafer typically 40% with BV 80 - 100V. Real yield higher as full depletion voltage is much lower

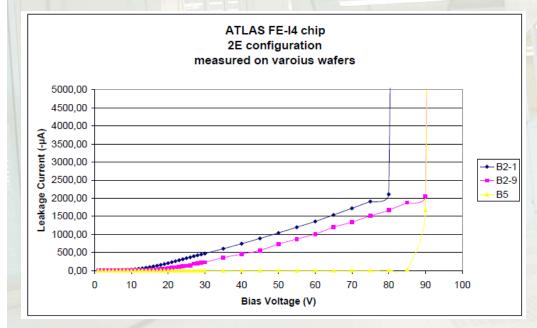

Measured IV-characteristics on ATLAS FE-I4 chips Total leakage from 20376 pixels (40752 electrodes) including MOS effect and possible bad electrodes

#### I-V measurements on FE-I4 chips from wafers B2-1, B2-9 (200 μm thick) and B5 (280 μm thick)

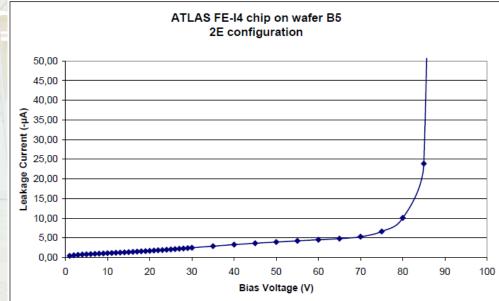

# I-V measurements on FE-I4 chip from wafer B5 (285 μm thick). Chip at wafer edge.

Active edge trench and electrodes not opened in upper left corner due to masking ring. Probably only  $\approx$  34000 electrodes opened (17000 pixels). < 100 pA / electrode in full depletion including MOS effect.

. . . . . .

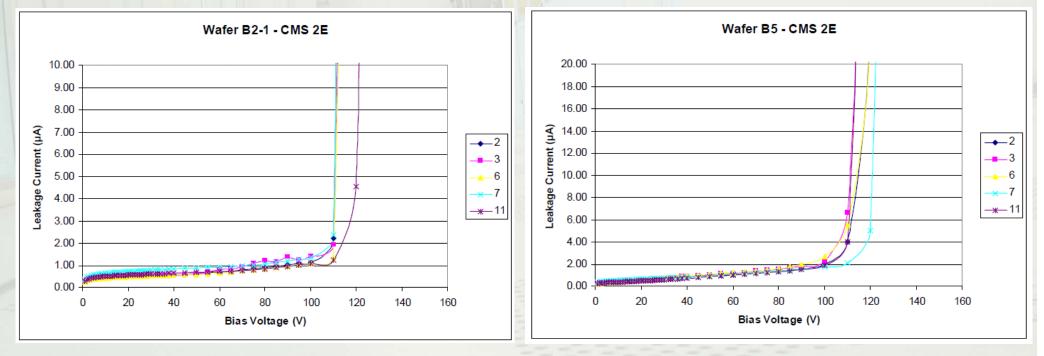

# Measured IV-characteristics CMS 1ROC chips 2E Configuration

5 good chip from wafer B2-1 (200 µm thick) and B5 (280 µm thick) Measured with test metallization which short circuits all pixels (n-electrodes). Total leakage includes contribution from "MOS" effect and possible bad pixels

Chip includes ≈ 2000 pixels (≈ 4000 n-electrodes)

Wafer B2-1 200 μm thick

Wafer B5 280 μm thick

ІСТ

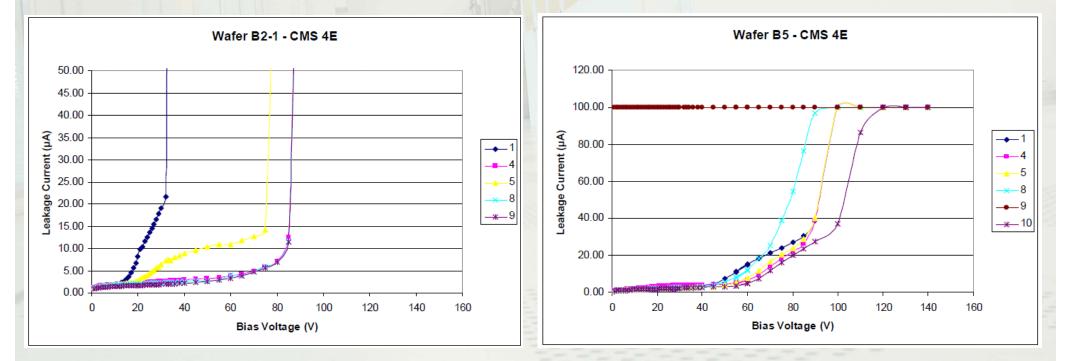

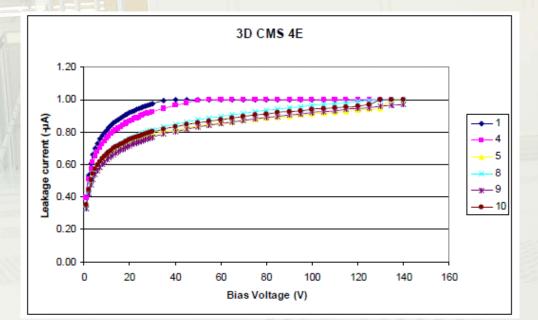

## Measured IV-characteristics CMS 1ROC chips 4E Configuration

5 chips from wafer B2-1 (200 µm thick) and B5 (280 µm thick) Measured with test metallization which short circuits all pixels (n-electrodes). Total leakage includes contribution from "MOS" effect and possible bad pixels

Chip includes ≈ 2000 pixels (≈ 8000 n-electrodes)

$\frac{\text{Wafer B2-1}}{200 \ \mu\text{m thick. Full depletion} < 5 \ \text{V}}$

Wafer B5 280 μm thick. Full depletion < 5 V

. . . . .

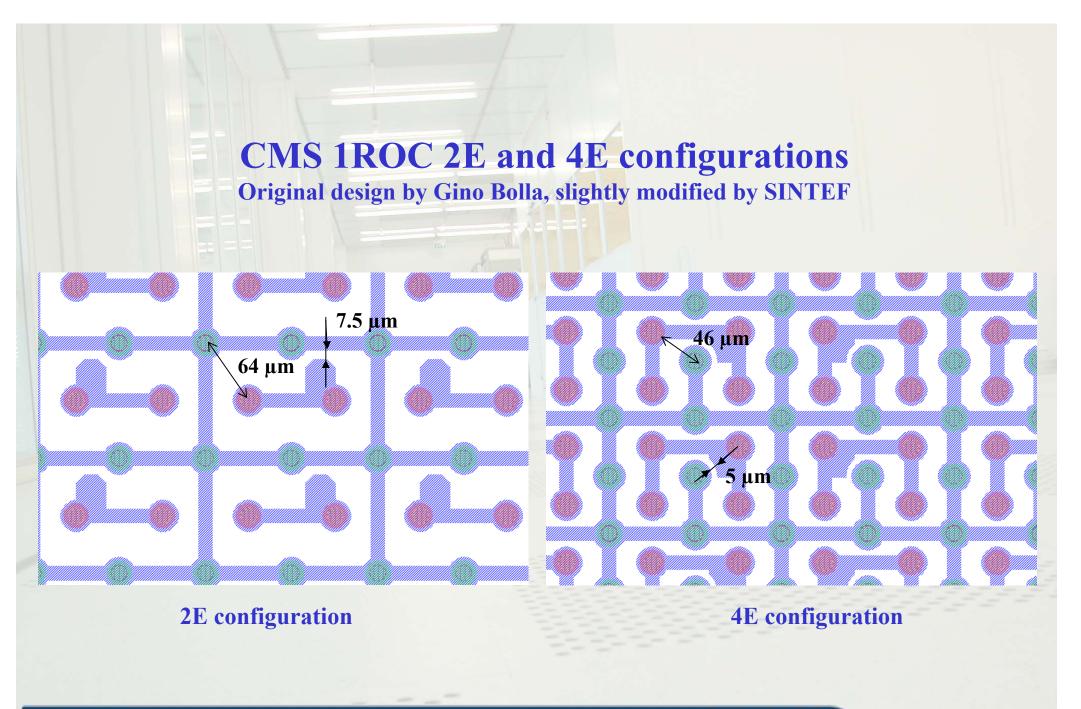

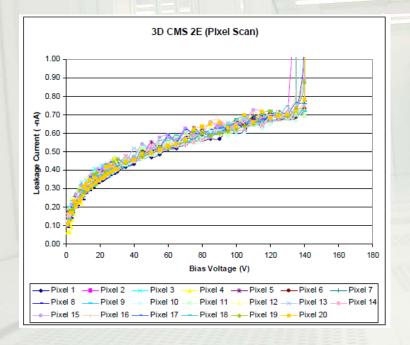

**CMS 1ROC 2E and 4E Configurations**

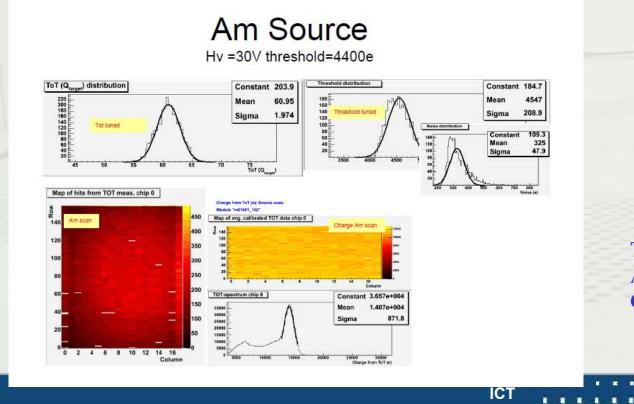

Single pixel IV-measurements on chips with final metal. Other pixels floating and measurement include pick up from adjacent pixels. Chip include ≈ 2000 pixels (4000 – 8000 n-electrodes)

#### **2E configuration**

IV-Measurement on 20 pixels from same chip. Very uniform leakage. Includes pick up from adjacent pixels

**4E configuration**

IV-Measurement on 6 pixels from same chip. Includes pick up from most of chip area

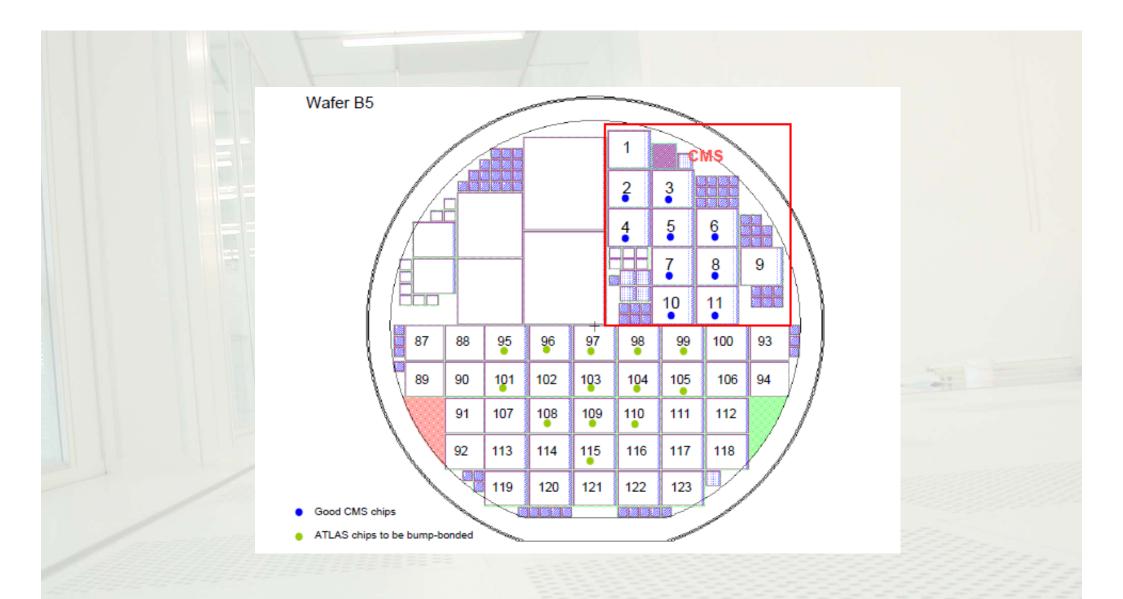

Wafer sent to IZM for Bump-bonding. Illustrates yield of FE-I3 and CMC 1ROC chips at wafer stage

ICT

.....

### **Conclusions and further work**

- Technically 2<sup>nd</sup> SINTEF 3D-lot did run smoothly. New IPROD DRIE tool gives high quality electrode holes and fast etch times. However, reliability of IPROD tool not convincing with 3 long down periods. Large delays compared to project plan

- 2. Process changes considerably reduced wafer stress and warping, improved electrode filling and lithography compared to first run. Low breakage and much improved wafer yield, 18 out of 23 wafers survived the process.

- Typical pixel average leakage current 0.5 to 1 nA in full depletion measured with a test metallization that short circuits all pixels (n-electrodes) and includes possible bad electrodes and a contribution from the "MOS" effect. Confirmed by single pixel measurements on chips with final metallization. Real pixel leakage probably ≤ 100 pA.

- 4. Medipix chips do not work. Seem to be no pn-junction. Must be investigated further.

### **Conclusions and further work**

- 5. 4 wafers sent to IZM for bump bonding:

2 wafers completed. Full FE-I3 assemblies made in Genoa.

Several bad assemblies, but at least one good.

Sent to CERN for beam test

- 6. Assembled unit successfully beam tested at CERN on 21.11.09, showed good Landau distribution

🕥 SINTEF

Test by Alessandro Rovani Claudia Gemme

### **Conclusions and further work**

- 7. 2 wafers deposited with UBM only. Have been returned to SINTEF for removal of support wafer and dicing by DRIE

- 8. Funds needed for common floor plan processing:

| Total processing cost | <b>??????</b> <sup>1)</sup> |

|-----------------------|-----------------------------|

| SINTEF internal funds | ≈ € 75k (TBC)               |

| Additional funding    | ??????                      |

Note 1: The processing cost will be evaluated within a few weeks