# A 2.5-D Integrated Data Logger for Measuring Extreme Accelerations

Jakob Gakkestad<sup>©</sup>, Tomas Sollund, Per Dalsjø, Bjørn Tveit, Maaike M. Visser Taklo, Daniel Nilsen Wright, Susanne Helland, Helge Kristiansen, and Christian Johnsen

Abstract—A very compact and rugged 2.5-D integrated data logger has been built and tested. The data logger is capable of measuring accelerations exceeding 70000 g. Microcontroller and flash memory as bare dies have been mounted onto a silicon interposer with through silicon vias using anisotropic conductive film and Au stud bump bonding. A microelectromechanical system accelerometer is mounted onto the interposer, using a robust customized flip-chip mounting approach. The interposer is mounted into a 16-pin leadless chip carrier package using isotropic conductive adhesive, where the conductive part is made of metallized polymer spheres. The ceramic package was mounted onto an application printed circuit board (PCB) with filters, power management, and an interface contact, using soldered plastic core solder balls (PCSBs). The diameter of the data logger is less than 9 mm, and the height is approximately 5 mm. The data logger fits within 12.7-mm (0.50 cal.) projectile, and acceleration measurements have been performed during firing, flight, and recovery. The measured accelerations have been verified by comparing the calculated projectile muzzle velocities with Doppler radar measurements.

Index Terms—2.5-D integration, acceleration, anisotropic conductive film (ACF), data logger, flip chip, harsh environment, isotropic conductive adhesive (ICA), plastic core solder balls (PCSBs), silicon interposer, through silicon via (TSV).

### I. INTRODUCTION

VER the last decade, tremendous research efforts have been made to miniaturize solutions for packaging of electronic devices. As the development cost for applicationspecific integrated circuits may not be economically viable

Manuscript received May 11, 2017; revised September 1, 2017; accepted October 13, 2017. Date of publication November 16, 2017; date of current version December 21, 2017. This work was supported by the European Defence Agency (EDA) through the project titled "Packaging 3D for Heterogeneous Rugged Electronics (PERU)," funded by France, Norway, and Italy and coordinated by Thales Avionics (Claude Sarno) in the frame of the EDA Project under Grant B-1336-IAP1-GP. Recommended for publication by Associate Editor C.-C. Lee upon evaluation of reviewers' comments. (Corresponding author: Jakob Gakkestad.)

- J. Gakkestad, T. Sollund, P. Dalsjø, and B. Tveit are with the Norwegian Defence Research Establishment (FFI), 2007 Kjeller, Norway (e-mail: jakob.gakkestad@ffi.no).

- M. M. V. Taklo and D. N. Wright are with SINTEF Digital, 0373 Oslo, Norway (e-mail: maaike.taklo@sintef.no).

- S. Helland is with Mosaic Solutions, 2013 Skjetten, Norway (e-mail: sh@mosaicsolutions.no).

- H. Kristiansen is with Conpart AS, 2013 Skjetten, Norway, and also with the Department of Structural Engineering, Norwegian University of Science and Technology, 7491 Trondheim, Norway (e-mail: helge@conpart.no).

- C. Johnsen is with Nammo, 2830 Raufoss, Norway (e-mail: christian.johnsen@nammo.com).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TCPMT.2017.2766263

in many cases, alternative affordable ways to integrate more functions into a smaller area have been explored. Use of stacked ICs and packages has become more common, often referred to as 2.5-D or 3-D packaging. Both 2.5-D and 3-D packaging allow heterogeneous integration of various components, making it possible to combine the best parts on the market into a single system [1]. For a 2.5-D integrated system, a passive interposer is used to allow dense assembly of active components and efficient routing. Through silicon vias (TSVs) can be fabricated in the interposer to enable routing between the top and bottom of the interposer. Xilinx utilizes this technology in its Virtex 7 field-programmable gate array products [2]. For a 3-D integrated system, active components are stacked directly; microelectromechanical system (MEMS) devices might, as an example, be directly connected to a microcontroller and a radio device using proper interconnect technologies and stacking of bare dies [3]. Products using 2.5-D or 3-D integrated solutions are used in a variety of applications spanning from consumer applications such as cellular phones to high-performance computing platforms, and there is ongoing research for using 3-D systems for harsh automotive applications [4].

The 2.5-D and 3-D packaging offer potential advantages, such as reduced footprint, weight, power consumption, high volumes, and cost, all of which are valuable for a range of military applications. As the integration level of electronic functions increases, it has become possible to integrate electronic functions, such as airburst capabilities, in medium caliber ammunitions (20–57-mm caliber ammunition) [5]. During firing and flight for this type of ammunition, the electronic parts are subjected to severe mechanical loads. For a 30-mm projectile, the peak setback acceleration is approximately 65 000 g and the centripetal acceleration due to the rotation of the projectile is 9000 g/mm out of center. For smaller calibers, the accelerations are normally higher than for the 30-mm caliber ammunition.

A useful tool for developing modern ammunition, e.g., adding airburst functionality, is a data logger for recording fuze signals during firing, flight, and recovery [6]–[8]. The data logger unit must be highly reliable, and data should be stored in a nonvolatile memory since the power source, typically a battery, may have insufficient power to preserve the data in RAM until the projectile is recovered and the read-out sequence accomplished. Due to the strict physical boundary conditions for this application, miniaturization is an absolute requirement.

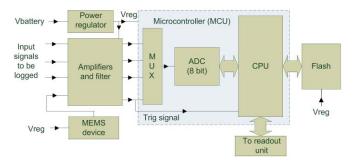

Fig. 1. Overview of the functional building blocks of the data logger.

The purpose of this paper was to investigate if a data logger, designed as a 2.5-D integrated system, was able to survive the extreme environments present in small and medium caliber ammunition. In addition, the use of metallized plastic core solder balls (PCSBs) as a replacement for traditional solder balls was to be tested. The PCSB provides a more flexible interconnect, giving improved reliability during thermal cycling and higher resistance toward mechanical shock. Since we had good experience with using a special isotropic conductive adhesive (ICA) as an alternative to solder for electronics in ammunition [9], we wanted to further investigate the use of this prototype ICA, made by Mosaic Solutions, based upon Conpart's metallized polymer spheres (MPS) for this application. The target was to build a data logger capable of measuring the setback acceleration of a 12.7-mm projectile. The peak setback acceleration for this small type of projectile was roughly estimated to 70000-100000 g. To the best of our knowledge, in situ acceleration measurements within a 12.7-mm projectile have not been reported earlier.

The rest of this paper is organized as follows. Section II presents an overview and short description of the data logger and its different packaging levels (PLs). Section III gives an overview over characterization tools and methods used in the development of the data logger. Sections IV–VII describe these levels in detail, where both traditional as well as novel interconnect technologies were investigated, culminating in the final data logger assembly and successful firing tests described in Section VII. Section VIII provides concluding remarks.

## II. DATA LOGGER DESIGN OVERVIEW

An overview of the functional building blocks of the data logger is presented in Fig. 1. The data logger consists of a microcontroller unit (MCU) with an internal multiplexer and analog-to-digital converter, a 256-kB nonvolatile RAM (NVRAM) (Flash) for data storage, a power regulator, and MEMS accelerometer capable of measuring the setback acceleration expected in a 12.7-mm projectile. Furthermore, it contains signal-conditioning circuitry (such as filters and amplifiers) for proper signal conditioning between the input signals and the MCU, and a connector for programming the data logger and reading out the recorded data.

In order to fit inside a 12.7-mm projectile, the diameter of the data logger must be less than 9 mm. This physical constraint governed the rest of the design, and components as small and energy-efficient as possible were needed to fulfill

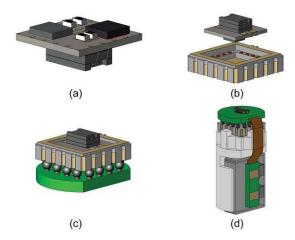

Fig. 2. Sketch of PLs as defined for the data logger. (a) PL0, consisting of the interposer with MCU, Flash, MEMS, and decoupling capacitors. (b) PL1, consisting of PL0 assembled into a ceramic leadless chip carrier package. (c) PL2, consisting of PL1 and WLCSP and passive components assembled to the front and back of the application board (lid not shown). (d) PL3, the complete data logger with battery.

this requirement, preferably as bare dies or as wafer-level chip scale packages (WLCSPs) when available. Furthermore, to better evaluate the different interconnect technologies proposed to be employed between the different parts of the data logger, the design process was split into four different PLs where each level went through stages of development, evaluation, and test before the final integration and assembly of the data logger. The details regarding the different PLs and the technologies that were used are described in Sections III–VII, but a brief overview will be given here.

Fig. 2(a) shows PL 0 (PL0), the very core of the data logger. On the top side of the 4 mm  $\times$  4 mm silicon interposer are bare die versions of the MCU and Flash memory (each measuring 1.4 mm  $\times$  1.4 mm) and decoupling capacitors. On the bottom is a bare die version of the MEMS high-shock accelerometer, measuring 1.7 mm  $\times$  2.5 mm  $\times$  1 mm. (The use of a packaged version of the same MEMS sensor would have increased the occupied volume by a factor of ten.) The interposer ensures proper internal signal routing and provides peripheral pads for interconnecting it to the next system level. TSVs provide electrical connections between the two sides of the interposer.

The interposer with its components is then flipped and mounted inside a ceramic package with outer dimensions of  $6.35 \text{ mm} \times 6.35 \text{ mm}$ , as shown in Fig. 2(b) (referred to as PL 1). The peripheral pads on the interposer ensure that all the signals of interest are available via the external pads on the ceramic package.

PL 2 (PL2), illustrated in Fig. 2(c), ensures interconnections between an application board and the ceramic package by using 720- $\mu$ m PCSBs from Conpart. For the active components on the application board, WLCSPs were used to reduce the occupied area as much as possible.

Finally, PL 3 (PL3), illustrated in Fig. 2(d), entails the complete assembly of the data logger ready to be placed inside a 12.7-mm projectile for acceleration measurements. The application board is designed as a rigid-flex system, where the flex cable connects an external battery to the power regulator of the system.

# III. TOOLS AND METHODS USED FOR CHARACTERIZATION

When using Kelvin structures for measuring electrical contact resistances, a Keithley 3706 system switch/multimeter was used. For two wire measurements, we used a Fluke 85 multimeter.

A Y. Cheetah X-ray machine from XYLON International was used for checking assembly of the different parts in the data logger. Both 2-D images and computed tomography scans were used.

For temperature shock cycle (TSC) tests, a CST130/2T thermal shock chamber from Angelantoni Industries was used, unless otherwise specified in the referenced publications.

For quasi-static acceleration tests, we used a Sorval WX Ultra 80 centrifuge. Centrifugation of test devices up to  $30\,000$  rpm results in a centripetal acceleration of  $1.4\times10^6$  m/s<sup>2</sup>, which corresponds to approximately 143 000 g. This centrifuge was also used for calibrating the sensitivity of the MEMS devices.

Dynamic acceleration tests were carried out using real test firings with suitable ammunition. In the first test, we used 30-mm projectiles, giving a peak setback acceleration when firing of approximately 65 000 g and a centripetal acceleration of approximately 9000 g/mm out of center. The setback acceleration lasts for approximately 4 ms, and the peak value occurs after approximately 2 ms. In the subsequent firing tests, we used 12.7-mm projectiles, having a peak setback acceleration of approximately 70 000 g and a centripetal acceleration of 19000 g/mm out of center. The acceleration lasts for approximately 2.5 ms, and the peak acceleration value is reached after 1.25 ms. All the projectiles were recovered in stacks of porous wallboards placed 100 m from the gun barrel. The speed of the projectiles was measured using a Weibel Doppler radar using a special software for muzzle velocity measurements at test firings. The radar operated at 10.4 GHz.

# IV. PACKAGING LEVEL 0: INTERPOSER WITH MCU, FLASH, AND MEMS ACCELEROMETER

### A. Interposer

The interposers were fabricated at SINTEF MiNaLab on 150-mm, 300- $\mu$ m-thick silicon wafers, where each die measured 4 mm  $\times$  4 mm. The TSVs were dry etched, insulated with a thermal oxide, and filled with doped poly-Si, and the routing and pads were made by etching a sputtered layer of aluminum.

On the bottom side of the interposer, pads to connect the MCU, Flash, and five decoupling capacitors were designed together with 16 I/O pads of Ø250  $\mu$ m along the periphery. These were located in correspondence with the pads inside the ceramic package, which is used at PL1 as housing (see Section V-A). On the top side of the interposer, two sets of pad configurations were designed for attaching the MEMS accelerometer in order to accommodate either the use of traditional die attach and wire bonds or a customized flip-chip solution (see Section IV-C).

The interposer wafers were postprocessed, where the pads on the wafers received an electroless Ni/electroless

Pd/immersion Au (ENEPIG) surface finish. This was required to achieve pads protruding sufficiently above the passivation layer (13.3  $\mu$ m) to facilitate anisotropic conductive film (ACF) mounting and for achieving solderable pads.

### B. MCU, Flash, and Decoupling Capacitors

One 200-mm, 725- $\mu$ m-thick silicon wafer with MCUs and one 300-mm, 775- $\mu$ m-thick silicon wafer with Flash devices were purchased. These wafers were received fully tested on wafer level (KGD), but the wafers were not diced. The wafers were grinded down to a thickness of 300  $\mu$ m after which they received an ENEPIG surface finish to achieve pads that were protruding 3.6  $\mu$ m above the passivation layer (measured by the UMB supplier using a Tencor profilometer).

The MCUs were mounted using ACF. For a precise and limited amount of ACF material per die, the film was laminated on wafer level prior to dicing and singulation.

Conpart supplied the ACF material containing their 5-μm MPS with a Ni/Au coating. Two different ACF film thicknesses of 18 and 25  $\mu$ m were tested. The 18- $\mu$ m-thick ACF film with 4000 particles/mm<sup>2</sup> is commercially available. Three versions of the 25- $\mu$ m-thick experimental ACF film were made with particle densities of 5000, 10000, and 20 000 particles/mm<sup>2</sup>. Due to the small pads of the designs in this paper, best results were achieved for the 25-µm-thick film and the highest particle density. More details on these experiments and early reliability testing of the assemblies made with the established process have been published in [10]. The reliability of ACF during humidity testing of test samples was considered as satisfactory for the application based on the results reported in [10], especially for interconnects where the MPS deformation was between 25% and 60%. However, when implementing ACF on real NVRAM devices, communication was not successful. Due to constraints with respect to time and resources, the root cause of this was not investigated.

Au stud bump bonding using a particularly thin Au wire was, therefore, tested for the assembly of the NVRAM. A 17.5-μm Au bond wire was needed due to the small size of the pads. Good results were quickly achieved, and it was, therefore, decided to use ACF for the MCU and Au stud bump bonding with thermocompression bonding for the NVRAM. As thermocompression bonding required a higher processing temperature than bonding with ACF, the NVRAM was bonded prior to the MCU. After bonding the MCU with ACF, underfilling of the NVRAM was done using Epo-Tek 353ND [11].

The mounting of the MCU and the Flash devices was performed at the University College of Southeast Norway, Horten, Norway, using a FinePlacer flip-chip bonder.

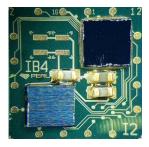

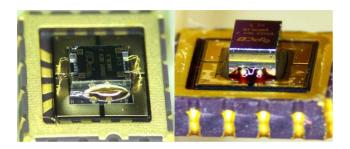

Decoupling capacitors were mounted manually onto the interposer, using ICA as interconnect. This was performed after the assembly of the MCU and Flash memory device. A photograph of an interposer with mounted MCU, Flash, and capacitors is shown in Fig. 3.

#### C. MEMS Accelerometer Interconnection

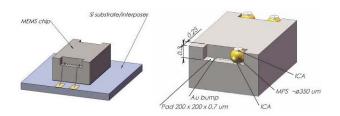

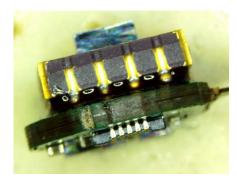

Two alternative methods for mounting the MEMS accelerometer were tested, which are illustrated in Fig. 4.

Fig. 3. Photograph of an interposer with mounted MCU, Flash, and capacitors.

Fig. 4. Mounting methods for the MEMS device. Left: die attach and wire bonding. Right: flip-chip assembly using PCSB and ICA.

The traditional method for connecting the MEMS device would be die attach combined with Au wire bonding. However, an alternative method, predicted to provide a more rugged assembly, was proposed. Au bumps were placed on the aluminum pads of the MEMS. ICA, based on MPS from Conpart, was deposited on these bumps, and PCSBs were assembled on top. After curing the ICA underneath the balls, ICA was deposited on the MEMS pad on the interposer, and the MEMS device was flipped and bonded to the interposer by curing the last deposited ICA.

Epo-Tek 353ND was used for the die attach process of the wire-bonded MEMS, and it was also used as an underfill material for the flip-chip bonded MEMS device. For testing of these two interconnect methods, we used "mechanically bad, electrically good" devices (as defined by the producer of the MEMS). Electrical connections could, therefore, be verified before and after dynamic acceleration tests, whereas the devices could not be used to measure the actual acceleration.

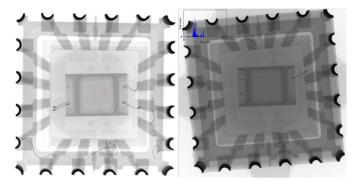

Two wire-bonded MEMS devices and two flip-chip mounted MEMS devices were exposed to dynamic acceleration tests using 12.7-mm projectiles. For redundancy, there were two wire bonds on each pad on the MEMS devices. The wire bonds were not covered by any protecting material since such a material could lose adhesion and rip off the bond wires when exposed to large acceleration forces. The mounted devices were placed in a ceramic package for support as shown in Fig. 5, and a suitable lid was placed over the ceramic package to protect the MEMS accelerometers from the potting material inside the projectile.

After recovery, the wire bonds were examined, both visually and by X-ray inspection. Several wire bonds had failed for each sample, as shown in Fig. 6. The flip-chip mounted MEMS devices, however, performed well during the test, and there were no measurable changes in the interconnections.

Fig. 5. Left: die attach and wire-bonded MEMS device. Right: flip-chip mounted MEMS device.

Fig. 6. X-ray of two wire-bonded MEMS devices after dynamic acceleration test. Left: four bond wires are missing. Right: seven bond wires are missing.

Fig. 7. ICA dots jetted onto the pads at the inner cavity of the ceramic package.

Therefore, this mounting method was used when assembling the complete data logger.

# V. PACKAGING LEVEL 1: ASSEMBLY OF INTERPOSER INTO CERAMIC PACKAGE

### A. Solder Paste and ICA Interconnect Tests

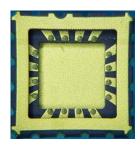

Three technologies for connecting the interposer to the inner cavity of the ceramic package were tested: solder paste (Almit Sn62U SS4M), prototype jet printable ICA developed by Mosaic Solutions, and soldered PCSB from Sekisui. The latter method is described in [12]. Both the solder paste and the ICA were jetted onto the inner pads of the ceramic package using an MY 500 machine. A ceramic package with jetted ICA is shown in Fig. 7. The interposer was mounted into the ceramic package using an MY 9 pick and place machine.

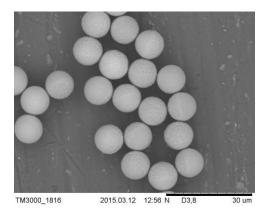

The conductive part of the ICA consists of  $10-\mu m$  Ag-coated MPS. An SEM image of the MPS is shown in Fig. 8. Properties of ICA based on MPS from Conpart are reported in [13] and [14].

Fig. 8. SEM images of MPS of the applied ICA. 10- $\mu$ m polystyrene spheres coated with a layer of 140-nm Ag.

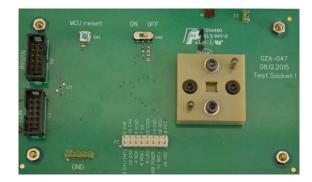

Fig. 9. Test socket on board used for measuring contact resistances between the interposer and ceramic package.

The interconnect solutions using solder paste or ICA were characterized by Kelvin measurements of the contact resistances before and after dynamic acceleration testing. Specially designed interposer dummy dies, which enabled Kelvin measurements of eight contact resistances per die, were mounted into the ceramic packages. A test socket and a corresponding printed circuit board (PCB), shown in Fig. 9, were designed for the tests. It is noteworthy that the measured contact resistances include the internal routing in the ceramic package as well as the pins in the test socket.

Five interposers were soldered into the ceramic packages, and the average initial contact resistance was measured to 0.187  $\Omega$  (N=40). Three samples were subjected to dynamic acceleration testing up to 65 000 g, and for two of these samples, the silicon interposers were broken into pieces. One sample survived the test, and the average contact resistance for this sample was 0.293  $\Omega$  (N=8). However, one of the resistances was an outlier with a resistance value above 1  $\Omega$ , which was probably caused by cracks in the soldering between the ceramic package and the interposer. If this value is excluded, the average value was 0.189  $\Omega$ , and the increase due to the test would then be insignificant.

Two interposers mounted into the ceramic packages with ICA were subjected to the same acceleration test. Prior to the test, the average contact resistance was 0.167  $\Omega$  (N=16), while afterward it was 0.226  $\Omega$  (N=16), representing an increase of 35.4%. However, since both the ICA-mounted interposers survived the tests and the increased resistance value

Fig. 10. PCB for testing PL1.

TABLE I

CONNECTIVITY TEST RESULTS FOR PL1

| Device no | MCU status | Flash status |

|-----------|------------|--------------|

| I6        | OK         | Not OK       |

| I7        | OK         | Not OK       |

| I8        | Not OK     | Not OK       |

| I9        | Not OK     | Not OK       |

| I10       | OK         | Not OK       |

| I11       | Partly     | Not OK       |

| I12       | Partly     | Not OK       |

| I25       | OK         | Not OK       |

| I26       | OK         | Not OK       |

| 127       | OK         | OK           |

| I28       | OK         | Not OK       |

| I29       | Not OK     | OK           |

was acceptable (less than 1  $\Omega$ ), this interconnect technology was chosen for the final data logger assembly. It should be noted that these tests were carried out without any use of underfill.

# B. MCU and Flash Connectivity Tests

In order to test the connectivity chain from the MCU and Flash memory, via the interposer and out to the outer pads of the ceramic package, 12 samples were assembled. Seven samples (represented as I6-I12) had MCU and Flash mounted with ACF, and five had MCU mounted with ACF and Flash mounted with Au stud bump bonding. For all the 12 samples, three decoupling capacitors were mounted with ICA. ICA was also used to interconnect the interposers to the inner cavity of the ceramic package. A PCB with a test socket was designed to test all the interconnects, as shown in Fig. 10. The devices under test were placed in the test socket, and all the pads from the ceramic package were routed to connectors on the board. When testing the MCU interconnects, the MCU was programmed to configure each relevant pin on the MCU as digital outputs. By generating a square wave signal train on each of these pins, which could be measured on the board connector, it provided a simple way of assessing each MCU pad that was successfully connected to the ceramic package. The Flash device was tested by writing data to it.

The test results are summarized in Table I. They show that for devices I8, I9, and I29, it was not possible to communicate with the MCU, and hence not possible to program them. For I11 and I12, communication was established and the

Fig. 11. Photographs from preparation for assembly of a ceramic package to an application board. Left: soldering of PCSBs. Right: use of jet printable ICA to attach PCSBs.

MCUs were properly programmed, but not all the pins toggled as intended, indicating faulty connections. It was not possible to establish contact with any of the ACF mounted Flash devices, and it is not clear why. However, two of the Au stud bump bonded Flash devices (I27 and I29) worked as intended. Unfortunately, the MCU failed to be programmed for the latter device. Hence, only device I27 had complete functionality. For the samples where only the MCU was properly connected, a firmware workaround was made where the sampled data would be stored in the MCU's internal memory rather than in the Flash. This limited the total amount of sampled values to 404 of 8-b resolution, but with a sampling frequency of 32 kHz, it provided 12.6 ms of data, sufficient to record the entire setback acceleration during a firing test. Based on these results, six complete data loggers were built, containing the devices I6, I7, I10, and I25-I27 (see Section VII). The I28 sample was not used since the pads for the MEMS connections were designed for wire bonding.

# VI. PACKAGING LEVEL 2: APPLICATION BOARD AND CERAMIC PACKAGE INTERCONNECTION

### A. Soldered and Adhesively Mounted PCSBs

Soldered versus adhesively mounted PCSBs were compared for connecting the ceramic package to the application board. The applied PCSBs were manufactured by Conpart and had a diameter of 720  $\mu$ m. The coating of the PCSBs comprises a 20- $\mu$ m-thick layer of Cu followed by a 3- $\mu$ m layer of Ni and finally a thin layer of Au. Besides establishing electrical contact between the ceramic package and the board, the balls ensured a sufficient standoff height to allow components to be assembled on both sides of the application board, also in the region below the ceramic package. The plastic core of the balls provided a mechanically more compliant solution than what would have been achievable using traditional solder balls. A test board for Kelvin measurements of the contact resistances was designed.

Fig. 11 shows photographs of the test board with soldered and adhesively mounted PCSBs before a ceramic package was mounted on the top of the PCSBs. It is noteworthy that the shape of the jetted ICA on top of the PCSBs remained practically unchanged after jetting. Two different volumes of solder and ICA were used, V1<sub>solder</sub>, V2<sub>solder</sub>, V1<sub>ICA</sub>, and V2<sub>ICA</sub>. The volume of solder paste or ICA was controlled by an MY 500 machine. For the solder paste, the V2<sub>solder</sub> was approximately 2.5 times the V1<sub>solder</sub>. The applied ICA was not calibrated for the jetting machine, and V2<sub>ICA</sub> was, therefore,

Fig. 12. Left: soldered PCSBs. Right: adhesively mounted PCSBs. Lid placed on top of the ceramics for later centering in the projectile.

#### TABLE II

RESISTANCES IN CONNECTION BETWEEN PCB-CERAMIC

PACKAGE-PCB USING SOLDERED OR ADHESIVELY MOUNTED

PCSB BEFORE AND AFTER DYNAMIC ACCELERATION TEST.

NOTE THAT THE SHOWN VALUE REPRESENTS

TWO MOUNTED PCSBS

| Amount of solder/ ICA | $R_{before}\left(\Omega\right)$ | $R_{after}\left(\Omega\right)$ |

|-----------------------|---------------------------------|--------------------------------|

| V1 <sub>solder</sub>  | 0.73                            | 0.72                           |

| $V2_{solder}$         | 0.67                            | 0.70                           |

| V1 <sub>ICA</sub>     | 0.93                            | 0.91                           |

| V2 <sub>ICA</sub>     | 0.78                            | 0.78                           |

not precisely 2.5 times  $V1_{ICA}$ , but it was certainly a larger volume than  $V1_{ICA}$ .

Assembled samples were tested electrically initially and were afterward exposed to more than 1000 thermal shock cycles, where the results are described in [15]. After the exposure to thermal shocks, some samples were subjected to dynamic acceleration tests exceeding 60 000 g (a 30-mm projectile was used in this case, housing several samples in each firing). A lid was made and placed on top of the ceramic package providing protection from the applied potting material and centering of the samples inside the projectile (see Fig. 12).

Two wire measurements were conducted between pads on the backside of the PCB, and measurements were done between pads 1 and 2, 1 and 3, and 1 and 4, then between pads 5 and 6, and so on. These measurements include the resistances of two PCSBs and all the wiring on the PCB and in the ceramic package. The results are summarized in Table II.

A total of 36 resistances for each group were measured. During the dynamic acceleration tests, one resistance for each group of the soldered PCSBs failed, whereas three of each group failed for the adhesively mounted PCSB. It is noteworthy that the resistance values were practically unchanged after being subjected to a very large mechanical force. The tests also showed that using a larger amount of solder paste or ICA gives a slightly lower contact resistance than using a smaller amount.

The results showed that soldered PCSBs provided the most reliable interconnection between the application board and the ceramic package as well as the lowest resistances. Soldering also offers the advantage of being more reworkable than adhesively mounted devices. No underfill material was used in these tests.

# B. Thermal Shock Cycle Tests of Underfill

When the data logger is inside a projectile, the gap between the application board and the ceramic package is intended to

Fig. 13. Underfill between ceramic package (top) and application board (bottom).

get filled by the potting material used inside the projectile. However, there is always a risk that the gap is not sufficiently filled, causing voids. Deflections might occur if voids are present due to the large forces involved during firing, possibly causing loss of electrical connection between the application board and the package. Epo-Tek 353 ND was, therefore, used as underfill between the application board and the ceramic package. Since the data logger has low power dissipation, a thermal underfill was not required. A photograph of a sample with underfill between the ceramic package and application board is shown in Fig. 13.

Underfill was also applied along the edges of the interposer inside the cavity of the ceramic package as a safety measure, reducing the mechanical loads on the ICA interconnects. Together with the flip-chipped and underfilled MEMS accelerometer, described in Section IV-C, these three underfilled interfaces were exposed to TSC to investigate possible changes or loss of adhesion between the parts.

During TSC, the underfill material may cause loss of contact between the application board and the ceramic package due to the differences in coefficient of thermal expansion (CTE) between the Epo-Tek 353ND, the ceramic package, and the application board. According to the manufacturer, Epo-Tek 353ND has a CTE of 54 and 206 ppm/K below and above the glass transition temperature (Tg), respectively. Tg is specified to be larger than 90 °C. Earlier dynamic mechanical analysis measurement of this epoxy showed that Tg could be around 112 °C.

After performing a dynamic acceleration test exceeding 70 000 g in a 12.7-mm projectile, samples with underfill were exposed to TSC between -55 °C and +125 °C, with 10 min dwell time and very short transition times (<30 s). Two flip-chip mounted MEMS devices (M1 and M2), seven interposers in ceramic packages with underfill along the inner cavity (U1–U7), and three samples with underfill between the application board and the ceramic package (S1–S3) were subjected to the cycling.

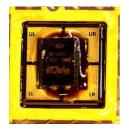

Fig. 14 shows one of the MEMS devices exposed to TSC. Electrical resistance could be measured between the corners on the interposer, represented as UL, LL, UR, and LR. Resistances were measured before the TSC started, then after 10, 50, and 100 cycles.

Table III summarizes the results, and shows that the TSC exposure had practically no effect on the measured resistance

Fig. 14. Underfilled MEMS device used in TSC.

| Samples | Initial value | 10 TSC     | 50 TSC     | 100 TSC    |

|---------|---------------|------------|------------|------------|

|         | $(\Omega)$    | $(\Omega)$ | $(\Omega)$ | $(\Omega)$ |

| M1 – M2 | 4695          | 4696       | 4711       | 4713       |

| U1 – U7 | 0.42          | 0.42       | 0.42       | 0.43       |

| S1 – S3 | 0.57          | 0.56       | 0.61       | 0.58       |

Fig. 15. Complete data logger, including battery.

values. The underfill material was, therefore, considered applicable for our data logger.

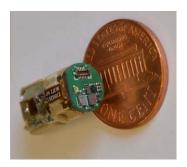

# VII. PACKAGING LEVEL 3: COMPLETE DATA LOGGER WITH BATTERY—ASSEMBLY AND TEST RESULTS

A total of six complete data loggers were assembled with the finally selected and tested interconnection technologies. A complete data logger is shown in Fig. 15, where the rigid-flex application board is connected to the ceramic package as well as to an external battery. The lid on the ceramic package and the battery holder, both machined in the thermoplastic PEEK material, was used for support and to ensure proper alignment for the data logger to fit into a 12.7-mm projectile. The components on the application board were soldered using the traditional surface mount technology and an Almit Sn62 SS4M solder paste. Similar to the test socket board shown in Fig. 10, a test board was designed specifically to test and verify the functionality of the application board prior to assembling it together with the ceramic package.

### A. Calibration of MEMS Accelerometer

Since we used unpackaged MEMS devices, the sensitivities had to be calibrated before the firing tests. This was done using quasi-static acceleration measurements. With a sampling frequency of 0.5 Hz, we ramped the centrifuge

#27

80

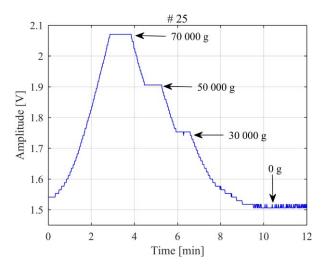

Fig. 16. Output voltage from sample #25 during accelerometer calibration.

Fig. 18. Measured setback acceleration when firing a 12.7-mm projectile.

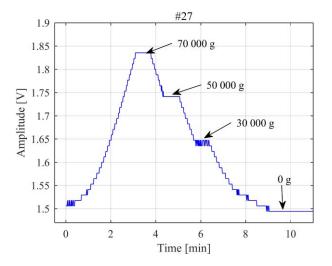

Fig. 17. Output voltage from sample #27 during accelerometer calibration.

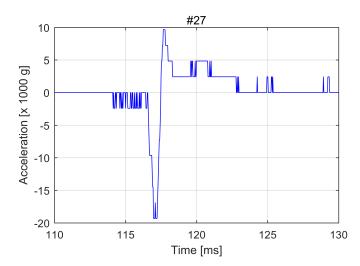

Fig. 19. Retardation when the projectile hits the porous wallboards.

to 23 000 rpm, corresponding to a centripetal acceleration of 70000 g, kept the acceleration stable for approximately 1 min, before decreasing the acceleration to 50000 g, and to 30000 g, before ending the calibration process. Due to problems with the assembly of the MEMS for data logger #7, the sensitivity from this device was very low, and due to an erroneous gain setting in the amplification stage, the sensitivities from #10 and #26 were low as well (the data logger numbering corresponds to the interposer numbering shown in Table I). The erroneous gain setting was corrected for samples #25 and #27. Figs. 16 and 17 show the results from the centrifuge tests for these two data loggers, from which the sensitivities of the sensors were found. One sample (#6) failed during the calibration test. The calibration test also revealed that the MEMS accelerometer behaved linearly within the sampling resolution for the tested range.

### B. Acceleration Measurements in 12.7-mm Projectile

Five calibrated data loggers were used for measuring the setback acceleration in the 12.7-mm firing test. The projectiles

were fired into a stack of porous wallboards at a 100-m distance, from which recovery of the data loggers could easily be made. During this test, one sample (#10) failed, and one sample had very low resolution (#7), while the other three samples gave good results. Fig. 18 shows the measured setback acceleration for data logger #27. The acceleration lasts for about 2.5 ms, after which the projectile exits the barrel and is experiencing a negative acceleration. The peak value is about 72 000 g and is reached 1.25 ms after firing. With the functioning Flash memory device on data logger #27, the retardation when hitting the wallboards could also be measured, shown in Fig. 19. First, a large retardation of nearly 20 000 g can be observed, whereupon the projectile starts tumbling, hence explaining the positive measured accelerations during the retardation phase.

Based on the acceleration measurements, the muzzle velocities were calculated and compared to the velocities measured by an on-site radar in order to investigate the accuracy of the experiments. The comparison is shown in Table IV. One source of inaccuracy is the internal system clock of the MCU,

TABLE IV

MEASURED AND CALCULATED MUZZLE VELOCITIES OF

THE PROJECTILES CONTAINING THE DATA LOGGERS

| Data logger # | Radar measurement | Calculated     |  |

|---------------|-------------------|----------------|--|

|               | (m/s)             | (m/s)          |  |

| 25            | 893               | $867 \pm 17.3$ |  |

| 26            | 894               | $904 \pm 18$   |  |

| 27            | 900               | $907 \pm 18.1$ |  |

causing the 32-kHz sampling frequency to have an accuracy of  $\pm 2\%$ . The variation in frequency will directly affect the calculated muzzle velocity. Taking this uncertainty into account, data loggers #26 and #27 provided a measured muzzle velocity within these uncertainty bounds, while data logger #25 measured a velocity 8.6 m/s outside of this bound.

#### VIII. CONCLUSION

We have fabricated a 2.5-D integrated data logger fitting into a 12.7-mm projectile with a traditional outline and successfully measured accelerations exceeding 70 000 g during a gun launch, resulting in a muzzle velocity and spin typical for this caliber. The small form factor was achieved using bare dies mounted onto a silicon interposer with TSVs, which again was mounted into a ceramic package using jet printable ICA. The ceramic package was mounted onto an application PCB with filters, power management, and an interface contact, using soldered PCSB. As a safety measure, underfill was applied between the application board and the ceramic package and along the edges of the interposer. TSC tests showed that the applied underfill did not degrade the system performance. The MEMS device was mounted onto the interposer using a customized flip-chip method since traditional wire bonding was not able to withstand the large mechanical forces during the dynamic acceleration test. Based on this paper, we have experienced that with use of underfill, or when the devices are well covered by the potting material inside the projectile, the interconnections are well preserved. In cases where it is not possible or desirable to use underfill, it is favorable to use a mechanically compliant interconnect technology such as PCSB or ICA based on the use of MPS. These interconnect technologies improve the ability to withstand mechanically and thermally induced forces. This paper included careful testing of individual interconnect technologies and a demonstrator with all these technologies integrated, and demonstrated that 2.5-D integration is suitable for very harsh environments.

### ACKNOWLEDGMENT

The authors would like to thank Dr. H. V. Nguyen at the University College of Southeast Norway, Horten, Norway, for doing the flip-chip mounting of the flash and the MCU parts, O. Opland (FFI) for his valuable efforts in assembling the data logger, and H. Jødahl (FFI) for manually mounting the MEMS devices.

#### REFERENCES

[1] R. Beica, "3D integration: Applications and market trends," in *Proc. Int. 3D Syst. Integr. Conf. (DIC)*, Aug. 2015, pp. TS5.1.1–TS5.1.7, doi: 10.1109/3DIC.2015.7334567.

- [2] K. Saban. (Dec. 2012). Stacked Silicon Interconnect Technology Delivers Breakthrough FPGA Capacity, Bandwidth, and Power Efficiency. [Online] Available: https://www.xilinx.com/support/ documentation/white\_papers/wp380\_Stacked\_Silicon\_Interconnect\_ Technology.pdf

- [3] P. Ramm et al., "3D integration technology: Status and application development," in Proc. ESSCIRC, Sep. 2010, pp. 9–16, doi: 10.1109/ ESSCIRC.2010.5619857.

- [4] E. Wachmann et al., "ATHENIS\_3D: Automotive tested high-voltage and embedded non-volatile integrated SoC platform with 3D technology," in Proc. Design, Autom. Test Eur. Conf. Exhibit. (DATE), Mar. 2016, pp. 894–899.

- [5] D. Andersen, "Scalable airburst fuze technology—Shaping the future," presented at the 56th Annu. Fuze Conf., Baltimore, MD, USA, May 2012. [Online]. Available: https://ndia.dtic.mil/2012/ fuze/2012fuze.html

- [6] P. C. Muller, E. F. Bukowski, G. L. Katulka, and P. Peregino, "Flight test and recovery of gun-launched instrumented projectiles using high-G onboard recording techniques," *IEEE Trans. Magn.*, vol. 43, no. 1, pp. 388–390, Jan. 2007, doi: 10.1109/TMAG.2006.887604.

- [7] G. Solak, T. Çelebi, and O. Yaşar, "Miniaturized on board data acquisition unit," presented at the 34th Eur. Telemetry Test Conf., Nuremberg, Germany, Jun. 2014, doi: 10.5162/etc2014/10.3.

- [8] M. Partridge and S. Curtis, "Shock-hardened penetrator data recorder to support hard-target fuze development," presented at the 59th Annu. Fuze Conf., Charleston, SC, USA, May 2016. [Online]. Available: https://ndia.dtic.mil/2016/fuze/2016fuze.html

- [9] J. Gakkestad, P. Dalsjo, H. Kristiansen, R. Johannessen, and M. M. V. Taklo, "Use of conductive adhesive for MEMS interconnection in ammunition fuze applications," *J. Micro/Nanolithography*, *MEMS*, *MOEMS*, vol. 9, no. 4, pp. 041108-1–041108-10, 2010, doi: 10.1117/1.3504691.

- [10] D. N. Wright et al., "Anisotropic conductive film for fine-pitch interconnects," in Proc. Int. Symp. Microelectron., vol. 2016. 2016, pp. 000044–000049, doi: 10.4071/isom-2016-TP23.

- [11] Epoxy Technology. EPO-TEK 353 ND Technical Data Sheet. Accessed May 13, 2014. [Online]. Available: http://www.epotek.com/ site/administrator/components/com\_products/assets/files/Style\_Uploads/ 353ND.pdf

- [12] M. M. V. Taklo *et al.*, "Reliability of plastic core solder balls in relation to formation of intermetallic compounds," in *Proc. 6th Electron. Syst.-Integr. Technol. Conf. (ESTC)*, Sep. 2016, pp. 1–6, doi: 10.1109/ESTC.2016.7764457.

- [13] J. Gakkestad, Z. Li, T. Helland, and C. P. Wong, "Thermomechanical properties of isotropic conductive adhesive filled with metallized polymer spheres," in *Proc. IEEE 15th Electron. Packag. Technol. Conf.* (EPTC), Dec. 2013, pp. 213–218, doi: 10.1109/EPTC.2013.6745715.

- [14] S. Jain et al., "Electrical properties of an isotropic conductive adhesive filled with silver coated polymer spheres," in Proc. 18th Eur. Microelectron. Packag. Conf. (EMPC), Sep. 2011, pp. 1–7.

- [15] J. Gakkestad et al., "Use of soldered or glued PCSB as interconnection between PCB and ceramic package in harsh environment," in Proc. Additional Conf. (Device Packag., HiTEC, HiTEN, CICMT), 2016, pp. 1–6, doi: 10.4071/2016-NOR-Gakkestad.

**Jakob Gakkestad** received the M.Sc. and Ph.D. degrees in electronics from the University of Oslo, Oslo, Norway, in 1985 and 1993, respectively.

In 1985, he joined SINTEF ICT (now SINTEF Digital), Oslo, as an ASIC Designer, focusing on the design of mixed signal ASIC in BiCMOS and CMOS technology. From 1997 to 2002, he was with Tandberg Data, Oslo, where he became a Manager of the Hardware Development Department. He was also a Senior Analog ASIC Designer at Chipcon, Oslo, (now TI). In 2003, he joined the Norwegian

Defence Research Establishment (FFI), Kjeller, Norway. From 2012 to 2013, he was a Research Scholar at Prof. C. P. Wong's Group, MSE, GeorgiaTech, Atlanta, GA, USA.

Tomas Sollund was born in Oslo, Norway, in 1982. He received the B.Sc. degree (First Class Hons.) in mathematics and engineering, control and communications option from Oueen's University, Kingston, ON, Canada, in 2006, and the M.Eng. degree in electrical engineering from McGill University, Montreal, QC, Canada, in 2009.

Since 2009, he has been a Research Scientist with the Norwegian Defence Research Establishment, Kjeller, Norway.

Daniel Nilsen Wright received the M.Chem. degree in chemical physics from Liverpool University, Liverpool, U.K., in 2001, and the Ph.D. degree in physics from the University of Oslo, Oslo, Norway, on the subject of antireflective coatings on silicon solar cells, in 2008.

In 2002, he did his military service at the Norwegian Defence Research Establishment (FFI), Kjeller, Norway, focusing on IR diodes. He focused on solar cells at REC ASA, Sandvika, Norway, until 2012. He is currently with the Advanced Packaging

and Interconnect Group, SINTEF Digital, Oslo.

Dalsjø received the M.Sc. degree in mechatronic engineering from The University of New South Wales, Sydney, NSW, Australia, in 2001, and the M.Sc. degree in electronic engineering specializing in microelectromechanical systems from the University of Oslo, Oslo, Norway, in 2007.

He was a Mechanical Engineer for several years. Since 2007, he has been a Scientist with the Norwegian Defence Research Establishment (FFI), Kjeller, Norway.

Susanne Helland received the M.Sc. degree in nanotechnology from the Norwegian University of Science and Technology, Trondheim, Norway, in 2011.

She has been a Project Manager and a Research Scientist with Mosaic Solutions, Skjetten, Norway,

Bjørn Tveit received the B.Sc. degree in electronics from the Oslo College of Engineering, Oslo, Norway, in 1977.

Since 1980, he has been an Electronic Engineer with the Norwegian Defence Research Establishment, Kjeller, Norway.

Helge Kristiansen received the M.Sc. and Ph.D. degrees in physics from the University of Oslo, Oslo, Norway, in 1988 and 1996, respectively.

From 1988 to 2004, he was with Microelectronic Packaging at SINTEF (previously Center for Industrial Research), Oslo. From 1999 to 2004, he was a part-time Senior Scientist at Chalmers University, Göteborg, Sweden. Since 2004, he has been with Conpart, Skjetten, Norway, and since 2016, he has been a Professor with the Norwegian University of Science and Technology, Trondheim, Norway.

Maaike M. Visser Taklo received the M.Sc. degree in physics from the Norwegian University of Science and Technology, Trondheim, Norway, in 1997, and the Ph.D. degree in physical electronics from the University of Oslo, Oslo, Norway, in 2002. Her thesis was titled "Wafer Bonding for MEMS."

She was with AME AS, Horten, Norway, focusing on the qualification of radiation sensors from 1997 to 1998. She was with the Department of Microsystems and Nanotechnology, SINTEF Digital, Oslo, from 1998. She is currently a Chief Scientist with

SINTEF Digital, where she is a Research Manager with the Department of Smart Sensor Systems, which she transferred to in 2010.

Christian Johnsen received the M.Sc. degree in electronics from the Norwegian University of Science and Technology, Trondheim, Norway, in 1995.

From 1996 to 2000, he was with Det Norske Veritas (now DNV GL), Høvik, Norway. From 2000 to 2002, he was an Instructor at Defense Engineering College, Fåberg, Norway. Since 2002, he has been with Research and Development, Nammo, Raufoss, Norway.